MC33880DW View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MC33880DW Datasheet PDF : 24 Pages

| |||

Freescale Semiconductor, Inc.

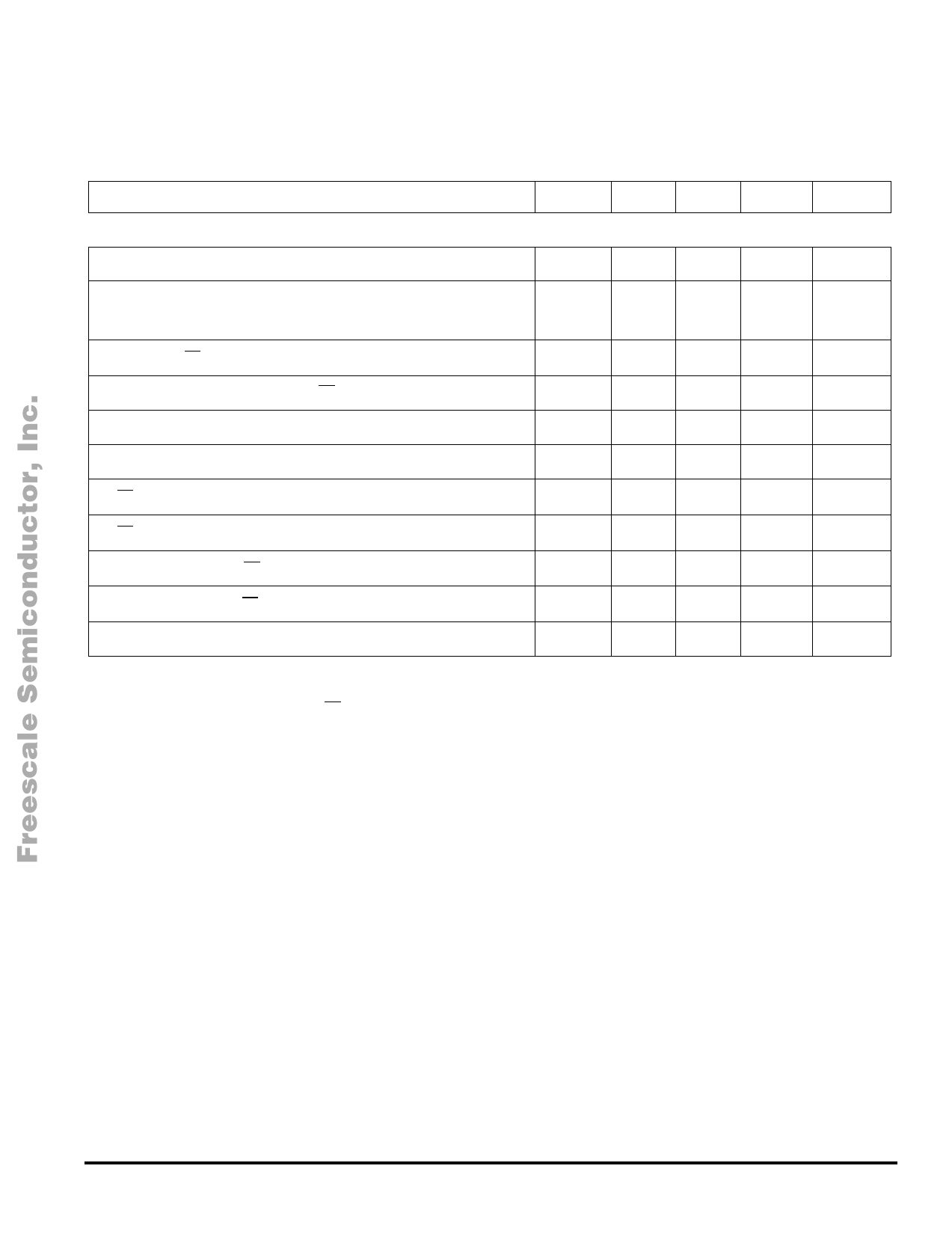

DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions of 4.75 V ≤ VDD ≤ 5.25 V, 9.0 V ≤ VPWR ≤ 16 V, -40°C ≤ TC ≤ 125°C unless otherwise

noted. Typical values, where applicable, reflect the parameter’s approximate average value with VPWR = 13 V, TA = 25°C.

Characteristic

Symbol

Min

Typ

Max

Units

DIGITAL INTERFACE TIMING

Recommended Frequency of SPI Operation

–

–

4.0

6.0

MHz

Required Low State Duration on VDD for Reset (Note 16)

VDD ≤ 0.2 V

tRESET

µs

–

4.0

10

Falling Edge of CS to Rising Edge of SCLK (Required Setup Time)

tLEAD

100

–

–

ns

Falling Edge of SCLK to Rising Edge of CS (Required Setup Time)

DI to Falling Edge of SCLK (Required Setup Time)

Falling Edge of SCLK to DI (Required Hold Time)

DI, CS, SCLK Signal Rise Time (Note 17)

tLAG

50

–

–

ns

tDI(su)

16

–

–

ns

tDI(HOLD)

20

–

–

ns

tR(DI)

–

5.0

–

ns

DI, CS, SCLK Signal Fall Time (Note 17)

tF(DI)

–

5.0

–

ns

Time from Falling Edge of CS to DO Low Impedance (Note 18)

tDO(EN)

–

–

60

ns

Time from Rising Edge of CS to DO High Impedance (Note 19)

tDO(DIS)

–

–

60

ns

Time from Rising Edge of SCLK to DO Data Valid (Note 20)

tVALID

–

25

60

ns

Notes

16. This parameter is guaranteed by design but is not production tested.

17. Rise and Fall time of incoming DI, CS, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

18. Time required for output status data to be available for use at DO pin.

19. Time required for output status data to be terminated at DO pin

20. Time required to obtain valid data out from DO following the rise of SCLK.

MOTOROLA ANALOG INTEGRATED CIRFCoUrITMDEoVrIeCEIDnAfoTArmation On This Product,

Go to: www.freescale.com

33880

11