UPD17217CT-XXX View Datasheet(PDF) - NEC => Renesas Technology

Part Name

Description

Manufacturer

UPD17217CT-XXX

UPD17217CT-XXX Datasheet PDF : 84 Pages

| |||

µPD17215, 17216, 17217, 17218

2.3.2 Function of stack

The address stack register stores a return address when the subroutine call instruction or table reference instruction (first

instruction cycle) is executed or when an interrupt is accepted. It also stores the contents of the address registers (ARs)

when a stack manipulation instruction (PUSH AR) is executed.

The WDOUT pin goes low if a subroutine call or interrupt exceeding 5 levels is executed.

The interrupt stack register (INTSK) saves the contents of the bank register (BANK) and program status word (PSWORD)

when an interrupt is accepted. The saved contents are restored when an interrupt return (RETI) instruction is executed.

INTSK saves data each time an interrupt is accepted, but the data stored first is lost if more than 3 levels of interrupts

occur.

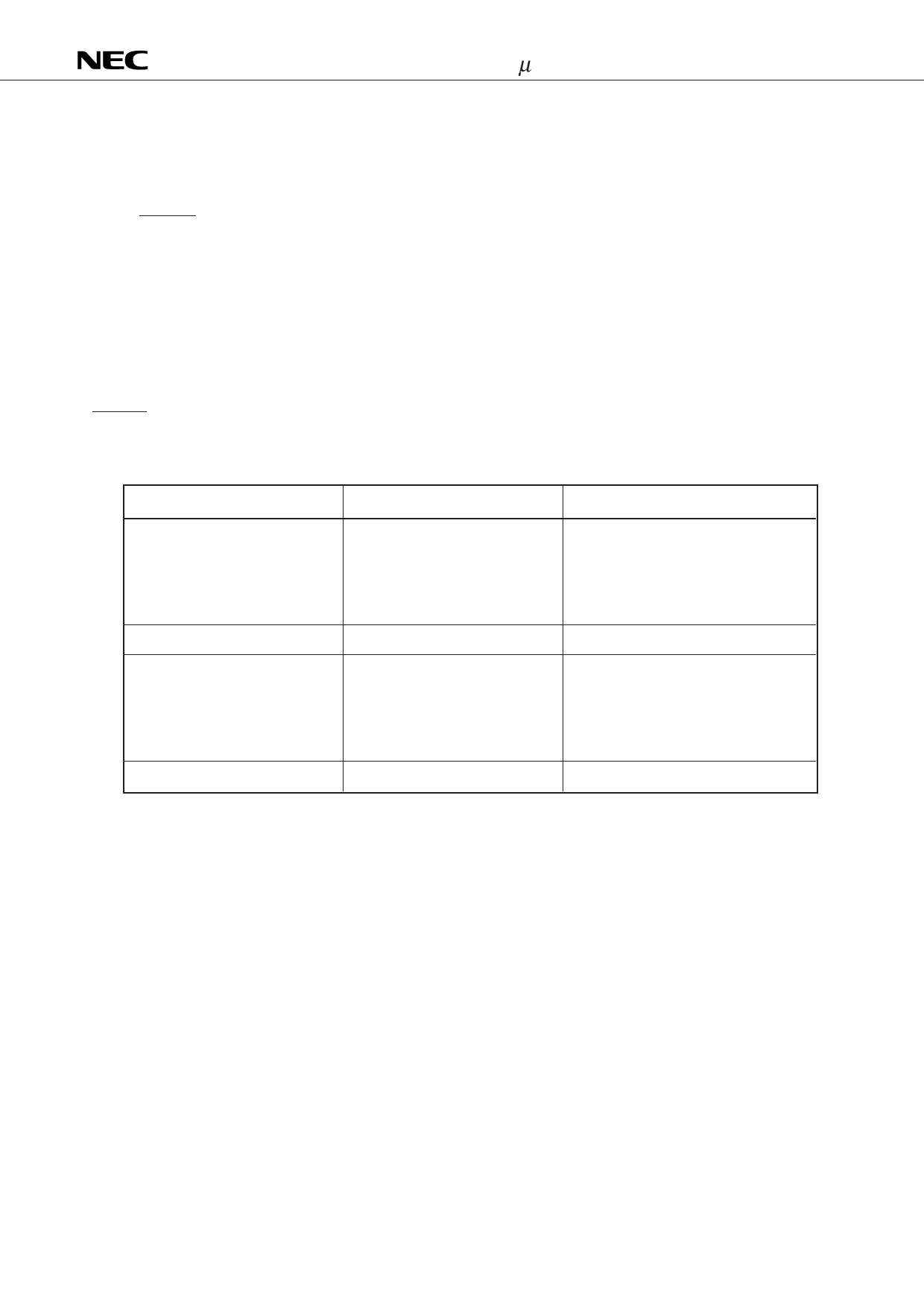

2.3.3 Stack Pointer (SP) and Interrupt Stack Pointer

Table 2-1 shows the operations of the stack pointer (SP).

The stack pointer can take eight values, 0H-07. Because there are only five stack registers available, however, the

WDOUT pin goes low if the value of SP is 6 or greater.

Table 2-1 Operations of Stack Pointer

Instruction

CALL addr

CALL @AR

MOVT DBF, @AR

(1st Instruction Cycle)

PUSH AR

When Interrupt Is Accepted

RET

RETSK

MOVT DBF, @AR

(2nd Instruction Cycle)

POP AR

RET1

Value of Stack Pointer (SP)

–1

–1

+1

+1

Counter of Interrupt Stack Register

0

–1

0

+1

13