AT89C5131A-M(2005) View Datasheet(PDF) - Atmel Corporation

Part Name

Description

Manufacturer

AT89C5131A-M Datasheet PDF : 184 Pages

| |||

PLL Programming

Divider Values

AT89C5130A/31A-M

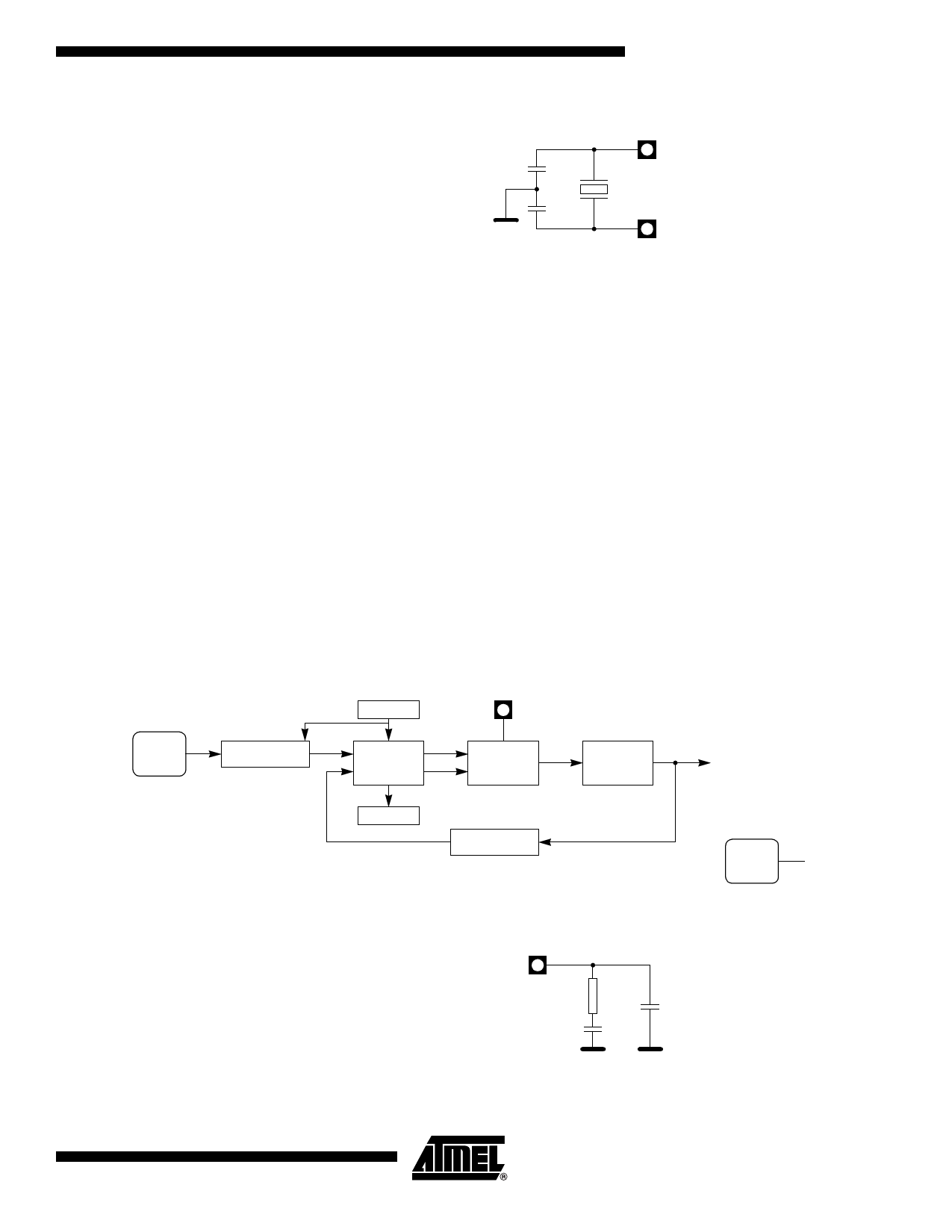

The PLL is programmed using the flow shown in Figure 9. As soon as clock generation

is enabled user must wait until the lock indicator is set to ensure the clock output is

stable.

Figure 9. PLL Programming Flow

PLL

Programming

Configure Dividers

N3:0 = xxxxb

R3:0 = xxxxb

Enable PLL

PLLEN = 1

PLL Locked?

LOCK = 1?

To generate a 48 MHz clock using the PLL, the divider values have to be configured fol-

lowing the oscillator frequency. The typical divider values are shown in Table 13.

Table 13. Typical Divider Values

Oscillator Frequency

R+1

N+1

3 MHz

16

1

6 MHz

8

1

8 MHz

6

1

12 MHz

4

1

16 MHz

3

1

18 MHz

8

3

20 MHz

12

5

24 MHz

2

1

32 MHz

3

2

40 MHz

12

10

PLLDIV

F0h

70h

50h

30h

20h

72h

B4h

10h

21h

B9h

15

4337C–USB–02/05