K4B4G1646Q View Datasheet(PDF) - Samsung

Part Name

Description

Manufacturer

K4B4G1646Q Datasheet PDF : 65 Pages

| |||

K4B4G1646Q

datasheet

Preliminary Rev. 0.5

DDR3L SDRAM

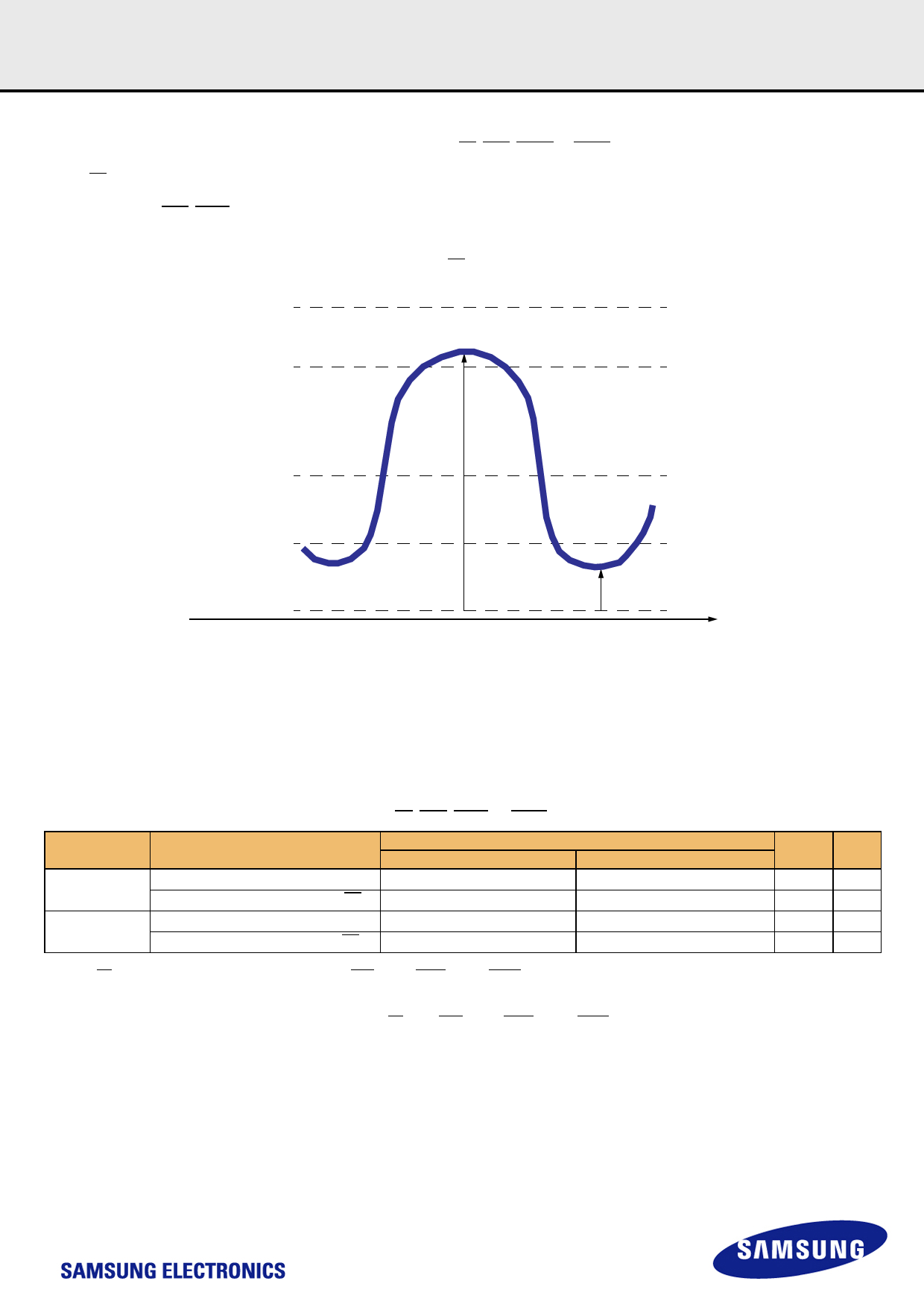

8.3.3 Single-ended requirements for differential signals

Each individual component of a differential signal (CK, DQS, DQSL, DQSU, CK, DQS, DQSL, or DQSU) has also to comply with certain requirements for

single-ended signals.

CK and CK have to approximately reach VSEHmin / VSELmax [approximately equal to the ac-levels { VIH(AC) / VIL(AC)} for ADD/CMD signals] in every

half-cycle.

DQS, DQSL, DQSU, DQS, DQSL have to reach VSEHmin / VSELmax [approximately the ac-levels { VIH(AC) / VIL(AC)} for DQ signals] in every half-cycle

proceeding and following a valid transition.

Note that the applicable ac-levels for ADD/CMD and DQ’s might be different per speed-bin etc. E.g. if VIH150(AC)/VIL150(AC) is used for ADD/CMD sig-

nals, then these ac-levels apply also for the single-ended signals CK and CK .

VDD or VDDQ

VSEH min

VSEH

VDD/2 or VDDQ/2

VSEL max

CK or DQS

VSS or VSSQ

VSEL

Figure 2. Single-ended requirement for differential signals

time

Note that while ADD/CMD and DQ signal requirements are with respect to VREF, the single-ended components of differential signals have a requirement

with respect to VDD/2; this is nominally the same. The transition of single-ended signals through the ac-levels is used to measure setup time. For single-

ended components of differential signals the requirement to reach VSELmax, VSEHmin has no bearing on timing, but adds a restriction on the common

mode characteristics of these signals.

[ Table 14 ] Single-ended levels for CK, DQS, DQSL, DQSU, CK, DQS, DQSL, or DQSU

Symbol

VSEH

VSEL

Parameter

Single-ended high-level for strobes

Single-ended high-level for CK, CK

Single-ended low-level for strobes

Single-ended low-level for CK, CK

DDR3-800/1066/1333/1600

Min

Max

(VDD/2)+0.175

NOTE3

(VDD/2)+0.175

NOTE3

NOTE3

(VDD/2)-0.175

NOTE3

(VDD/2)-0.175

Unit NOTE

V

1, 2

V

1, 2

V

1, 2

V

1, 2

NOTE :

1. For CK, CK use VIH/VIL(AC) of ADD/CMD; for strobes (DQS, DQS, DQSL, DQSL, DQSU, DQSU) use VIH/VIL(AC) of DQs.

2. VIH(AC)/VIL(AC) for DQs is based on VREFDQ; VIH(AC)/VIL(AC) for ADD/CMD is based on VREFCA; if a reduced ac-high or ac-low level is used for a signal group, then the

reduced level applies also here

3. These values are not defined, however the single-ended signals CK, CK, DQS, DQS, DQSL, DQSL, DQSU, DQSU need to be within the respective

limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot

Specification"

- 16 -