S25FL127SABMHI003(2005) View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

S25FL127SABMHI003 Datasheet PDF : 131 Pages

| |||

S25FL127S

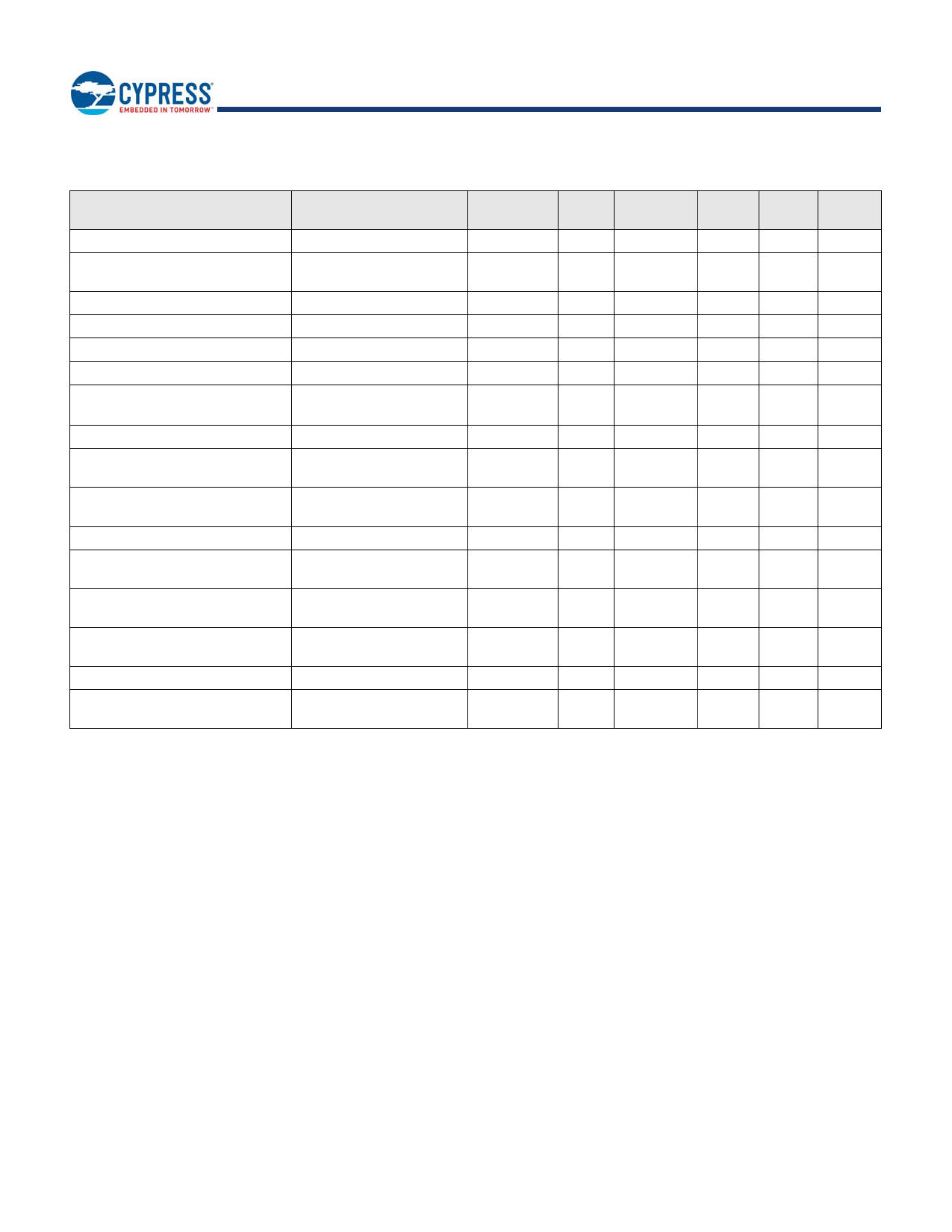

Table 3.2 Interface States Summary with IO3 / RESET# Enabled

Interface State

Power-Off

Low Power Hardware Data

Protection

Power-On (Cold) Reset

Hardware (Warm) Reset — Non-

Quad Mode

Hardware (Warm) Reset — Quad

Mode

Interface Standby

Instruction Cycle (Legacy SPI)

Single Input Cycle

Host to Memory Transfer

Single Latency (Dummy) Cycle

Single Output Cycle Memory to

Host Transfer

Dual Input Cycle Host to Memory

Transfer

Dual Latency (Dummy) Cycle

Dual Output Cycle Memory to Host

Transfer

QPP Address Input Cycle Host to

Memory Transfer

Quad Input Cycle Host to Memory

Transfer

Quad Latency (Dummy) Cycle

Quad Output Cycle Memory to Host

Transfer

Legend

Z = no driver - floating signal

HL = Host driving VIL

HH = Host driving VIH

HV = either HL or HH

X = HL or HH or Z

HT = toggling between HL and HH

ML = Memory driving VIL

MH = Memory driving VIH

MV = either ML or MH

VCC

<VCC (low)

<VCC (cut-off)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

VCC (min)

SCK

CS#

X

X

X

X

X

HH

X

X

X

HH

X

HH

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HT

HL

HOLD# /

IO3

X

X

X

HL

HL

X

HH

HH

HH

HH

HH

HH

HH

X

HV

X

MV

WP# /

IO2

X

X

X

X

X

X

HV

X

X

X

X

X

X

X

HV

X

MV

SO /

IO1

Z

Z

Z

Z

SI / IO0

X

X

X

X

Z

X

Z

X

Z

HV

Z

HV

Z

X

MV

X

HV

HV

X

X

MV

MV

X

HV

HV

HV

X

X

MV

MV

Document Number: 001-98282 Rev. *F

Page 21 of 130