IDT79R4650-100DP(2000) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-100DP

(Rev.:2000)

(Rev.:2000)

IDT79R4650-100DP Datasheet PDF : 25 Pages

| |||

IDT79RC4650™

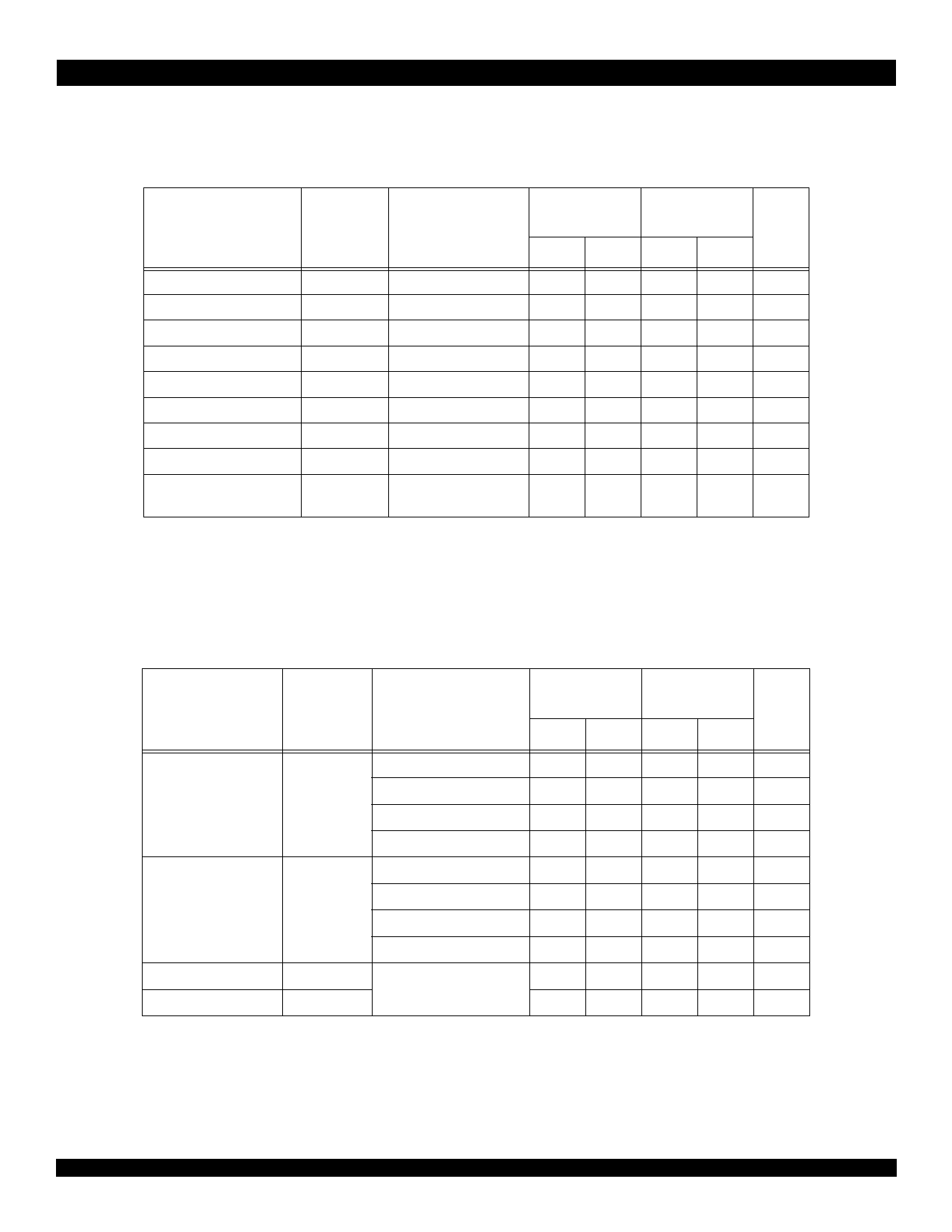

$&#HOHFWULFDO#&KDUDFWHULVWLFV#³#&RPPHUFLDO#7HPSHUDWXUH#5DQJH³57983

(VCC=5.0V ± 5%; TCASE = -0°C to +85°C)

&ORFN#3DUDPHWHUV³57983

3DUDPHWHU

6\PERO

7HVW#&RQGLWLRQV

57983

4330+]

0LQ 0D[

57983

4660+]

0LQ 0D[

8QLWV

Pipeline clock frequency

MasterClock HIGH

MasterClock LOW

MasterClock Frequency1

MasterClock Period

Clock Jitter for MasterClock

MasterClock Rise Time

MasterClock Fall Time

ModeClock Period

PClk

tMCHIGH

tMCLOW

—

tMCP

tJitterIn2

tMCRise2

tMCFall2

tModeCKP2

—

50

Transition ≤ tMCRise/Fall 4

Transition ≤ tMCRise/Fall 4

—

25

—

20

—

—

—

—

—

—

—

—

1. Operation of the RC4650 is only guaranteed with the Phase Lock Loop enabled.

2. Guaranteed by design.

100

50

—

3

—

3

50

25

40

15

±250 —

5

—

5

—

256* —

tMCP

133

MHz

—

ns

—

ns

67

MHz

40

ns

±250 ps

4

ns

4

ns

256* ns

tMCP

6\VWHP#,QWHUIDFH#3DUDPHWHUV³57983

(VCC=5.0V ± 5%; TCASE = 0°C to +85°C)

Note: Timings are measured from 1.5V of the clock to 1.5V of the signal.

3DUDPHWHU

6\PERO 7HVW#&RQGLWLRQV#

Data Output1

tDO = Max

mode14..13 = 10 (fastest)

mode14..13 = 11 (85%)

mode14..13 = 00 (66%)

Data Output Hold

tDOH3

mode14..13 = 01 (slowest)

mode14..13 = 10

mode14..13 = 11

mode14..13 = 00

mode14..13 = 01

Data Setup

Data Hold

tDS

trise = 5ns

tDH

tfall = 5ns

1. Capacitive load for all output timings is 50pF.

2. Guaranteed by design.

3. 50pf loading on external output signals, fastest settings

57983

4330+]

0LQ

1.02

0D[

9

2.02

12

1.0

—

5.5

—

2

—

57983

4660+]

0LQ

1.02

0D[

9

2.0

12

1.0

—

4.5

—

1.5

—

8QLWV

ns

ns

ns

ns

ns

14 of 25

March 28, 2000