BU1425AK View Datasheet(PDF) - ROHM Semiconductor

Part Name

Description

Manufacturer

BU1425AK Datasheet PDF : 32 Pages

| |||

Multimedia ICs

BU1425AK / BU1425AKV

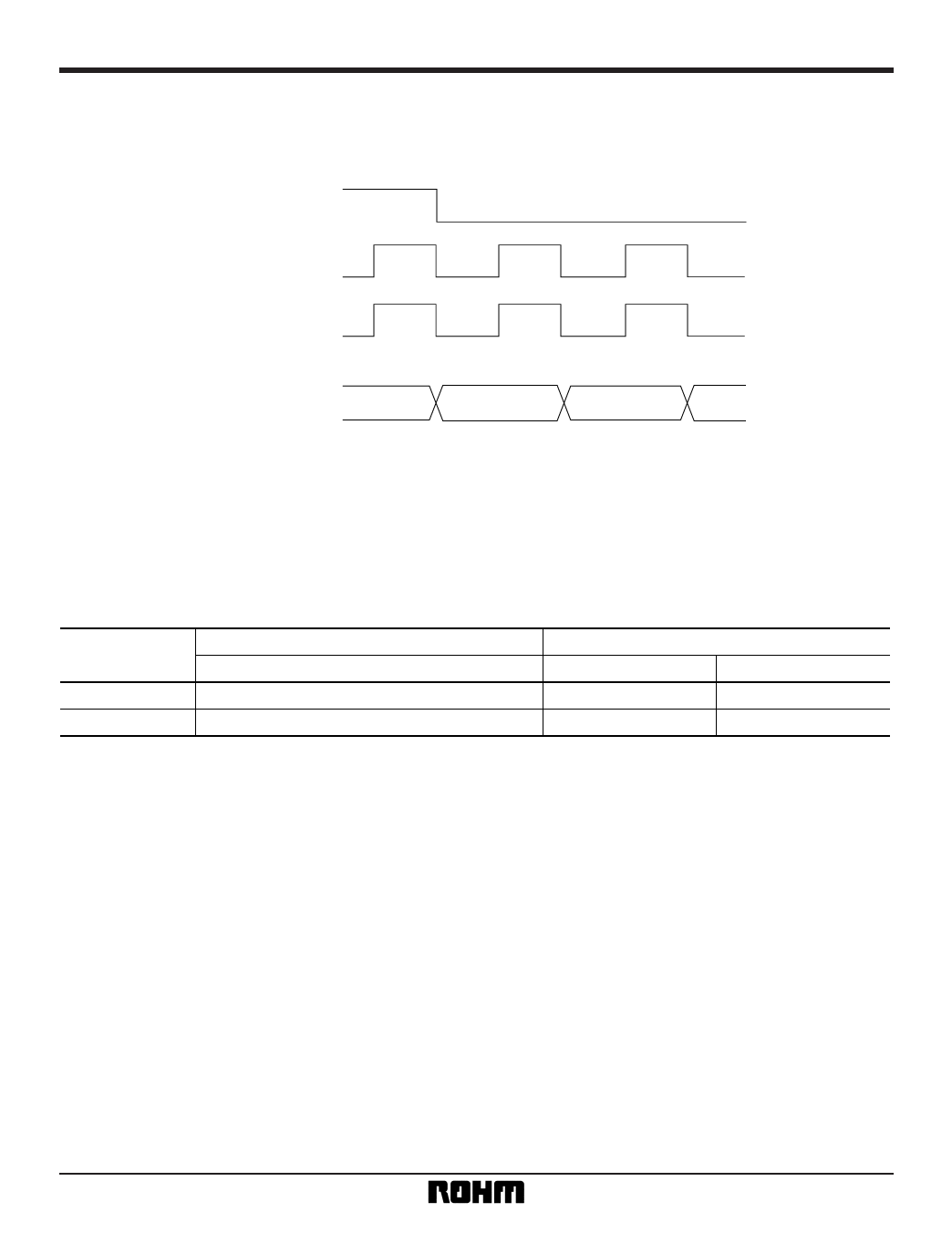

Also, setting the CLKSW pin to HIGH enables the fre-

quency of the external clock to be used as BCLK, the

internal clock, just as it is. Since the data is read to the

BU1425AK / AKV at the rising edge of BCLK at this

time as well, data should be input as shown in Fig. 4.

The relationship with HSY is also as shown in Fig. 4.

HSY

VCLK

Internal clock (BCLK)

Input data

Fig. 4 Illustration of clock timing (CLKSW is HIGH)

With the BU1425AK / AKV, the sub-carrier (burst) fre-

quency is generated using the internal clock. For this

reason, the frequencies used in the various modes are

limited, so those frequencies should be input (see Table

7 below).

Table 7: BU1425AK / AKV clock input frequency settings

CLKSW Pin

0

1

Video-CD Mode

Same for NTSC / PAL / PAL60

27.000MHz

13.500MHz

CD-G Mode

NTSC

PAL / PAL60

28.636MHz

28.3750MHz

14.318MHz

14.1875MHz

5) Synchronization signals

The BU1425AK / AKV has an "Encoder Master" mode in

which synchronization signals are output, and an

"Encoder Slave" mode in which synchronization signals

are input from an external source and used to achieve

synchronization. These modes are switched at the

SLABEB pin. When the SLABEB pin is LOW, the Slave

mode is in effect, and when HIGH, the Master mode is in

effect.

In the Master mode, the HSY and VSY pins serve as out-

put, with horizontal synchronization signals (HSYNC)

being output from the HSY pin and vertical synchroniza-

tion signals (VSYNC) from the VSY pin. At this time, the

reference timing for synchronization signal output is

determined at the rising edge of the RSTB pin. Output is

obtained in accordance with the specified mode (NTSC,

PAL, or PAL60, interlace or non-interlace). Output in the

14

non-interlace mode, however, is output only under "Odd"

field conditions (the falling edges of Hsy and Vsy are the

same).

In the Slave mode, the HSY and VSY pins serve as input,

and horizontal synchronization signals (HSYNC) should

be input to the HSY pin and vertical synchronization sig-

nals (VSYNC) to the VSY pin. The input synchronization

signals at this time should be input in accordance with

the specified mode. With the BU1425AK / AKV, field dis-

tinction between odd and even fields is made automati-

cally for each field when interlace input is used. With the

BU1425AK, all synchronization signals are treated as

negative polarity signals (signals for which the sync inter-

val goes LOW). When using the non-interlace mode,

operation is normally carried out under odd field condi-

tions (the falling edges of Hsy and Vsy are simultane-

ous).