LA70100M View Datasheet(PDF) - SANYO -> Panasonic

Part Name

Description

Manufacturer

LA70100M Datasheet PDF : 16 Pages

| |||

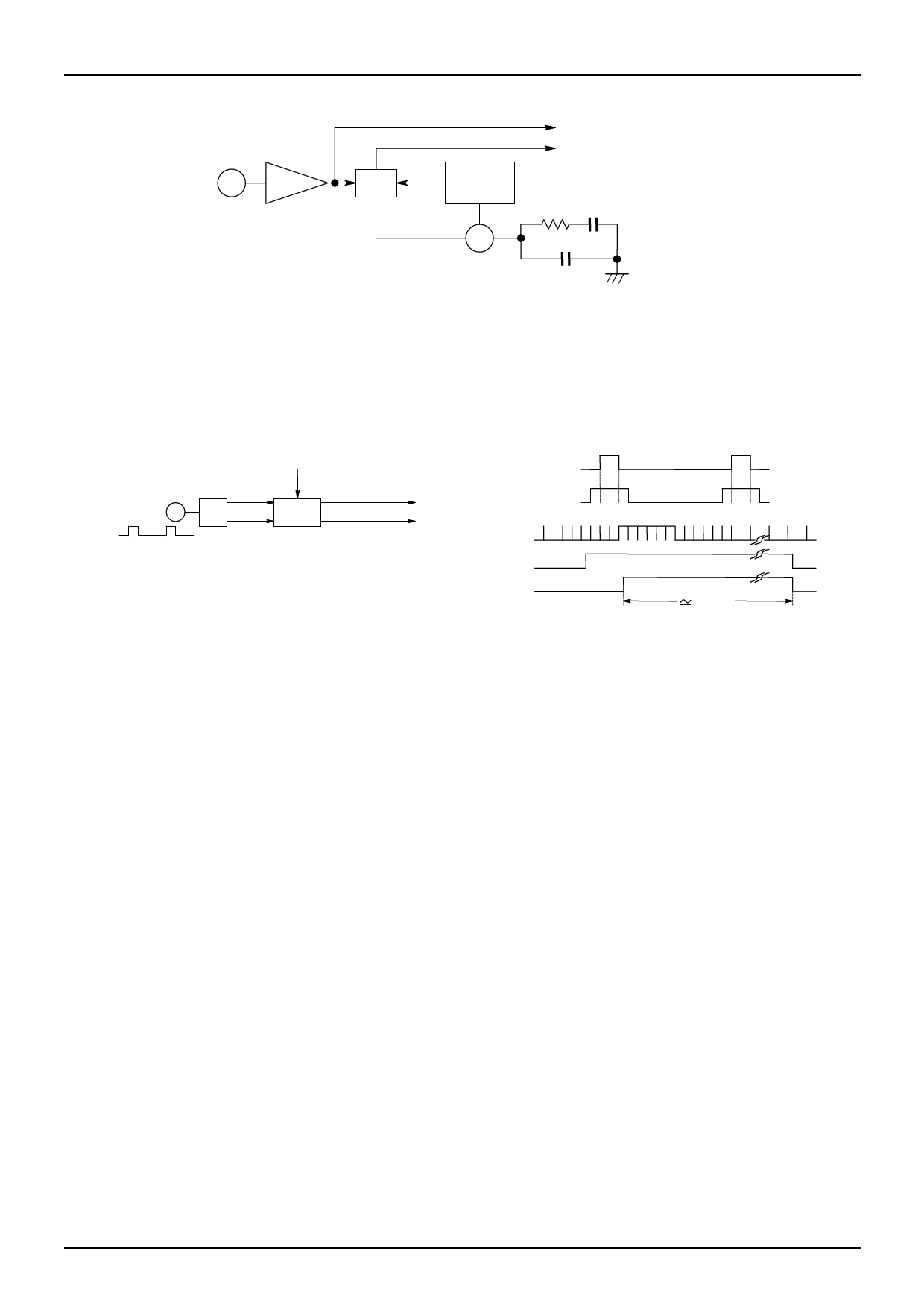

(3) CLK INPUT, AFC

LA70100M

for BELL ADJUST CLOCK

2

BUFF

4.43MHz

CLOCK

AFC

4.43MHz

VCO

for EACH FILTER ADJUST

3

Fig.3

Input a frequency of 4.433619MHz sine wave or rectangle waveform signal of PAL fsc to CLK input terminal. This signal is

used for automatically adjusting the BELL filter and generating timing pulse for AFC and for sync gate. AFC circuit

automatically adjusts the frequency characteristics for each BPF.

(4) SYNC GATE CIRCUIT

4.43MHz

CLOCK

SYNC GATE/MUTE

Composite sync C.SYNC

SECAM DET SAMPLE HOLD-1, 2

29

SYNC

SEPA

CONTROL

LOGIC

V.SYNC

BELL ADJUST

SECAM DET SAMPLE HOLD-3

C.sync

SYNC GATE

MUTE

C.sync

V-MUTE

BELL ADJUST

GATE

Fig.4

700µs

Vertical sync signal is extracted by a synchronous separate circuit from Composite Sync signal that has been input from Pin

29, and is conducted to BELL/A-BELL filter automatic adjusting circuit. Additionally, SYNC GATE pulse and sample hold

pulse are generated by the logic circuit.

(5) BGP generator circuit

BGP is used for killer circuit in REC Mode, AGC circuit in PB Mode, and SECAM discrimination circuit.

In BP Mode, AGC circuit detects the scale of the signal of BGP duration (ID) so that the output of 4 times multiplier circuit be

constant. In SECAM discrimination circuit, BGP is used for making the S/H pulse (SP9, SP2 in Figure 9) mentioned later.

Controlling Pin 4 can convert the timing for Composite Sync that is input to Pin 27. The width of BGP is determined by the

constant of the inside of IC to about 2.5 µs. And BGP timing can be monitored by Pin 28 in test mode (Pin 9 voltage = 5V).

No.7204-8/16