RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

4 Hardware Overview

The RM7000 offers a high-level of integration targeted at high-performance embedded

applications. The key elements of the RM7000 are briefly described below.

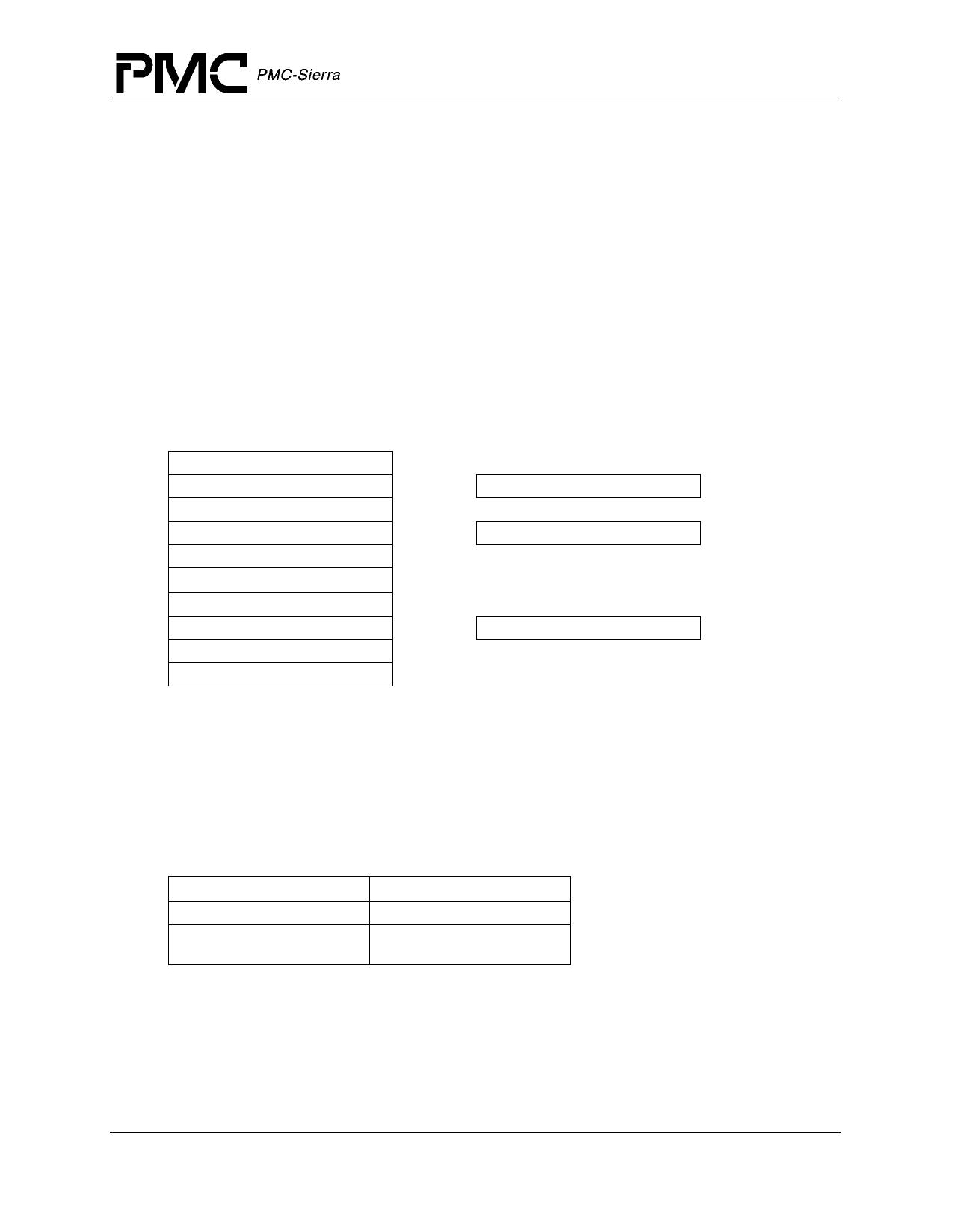

4.1 CPU Registers

Like all MIPS ISA processors, the RM7000 CPU has a simple, clean user visible state consisting

of 32 general purpose registers (GPR), two special purpose registers for integer multiplication and

division, and a program counter; there are no condition code bits. Figure 2 shows the user visible

state.

Figure 2 CP0 Registers

General Purpose Registers

63

0

0

r1

r2

•

•

•

•

r29

r30

r31

Multiply/Divide Registers

63

0

HI

63

0

LO

Program Counter

63

0

PC

4.2 Superscalar Dispatch

The RM7000 has an efficient symmetric superscalar dispatch unit which allows it to issue up to

two instructions per cycle. For purposes of instruction issue, the RM7000 defines four classes of

instructions: integer, load/store, branches, and floating-point. There are two logical pipelines, the

function, or F, pipeline and the memory, or M, pipeline. Note however that the M pipe can execute

integer as well as memory type instructions.

Table 1 Instruction Issue Rules

F Pipe

M Pipe

one of:

one of:

integer, branch, floating-point, integer, load/store

integer mul, div

Figure 3 is a simplification of the pipeline section and illustrates the basics of the instruction issue

mechanism.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

12

Document ID: PMC-2002175, Issue 1