RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

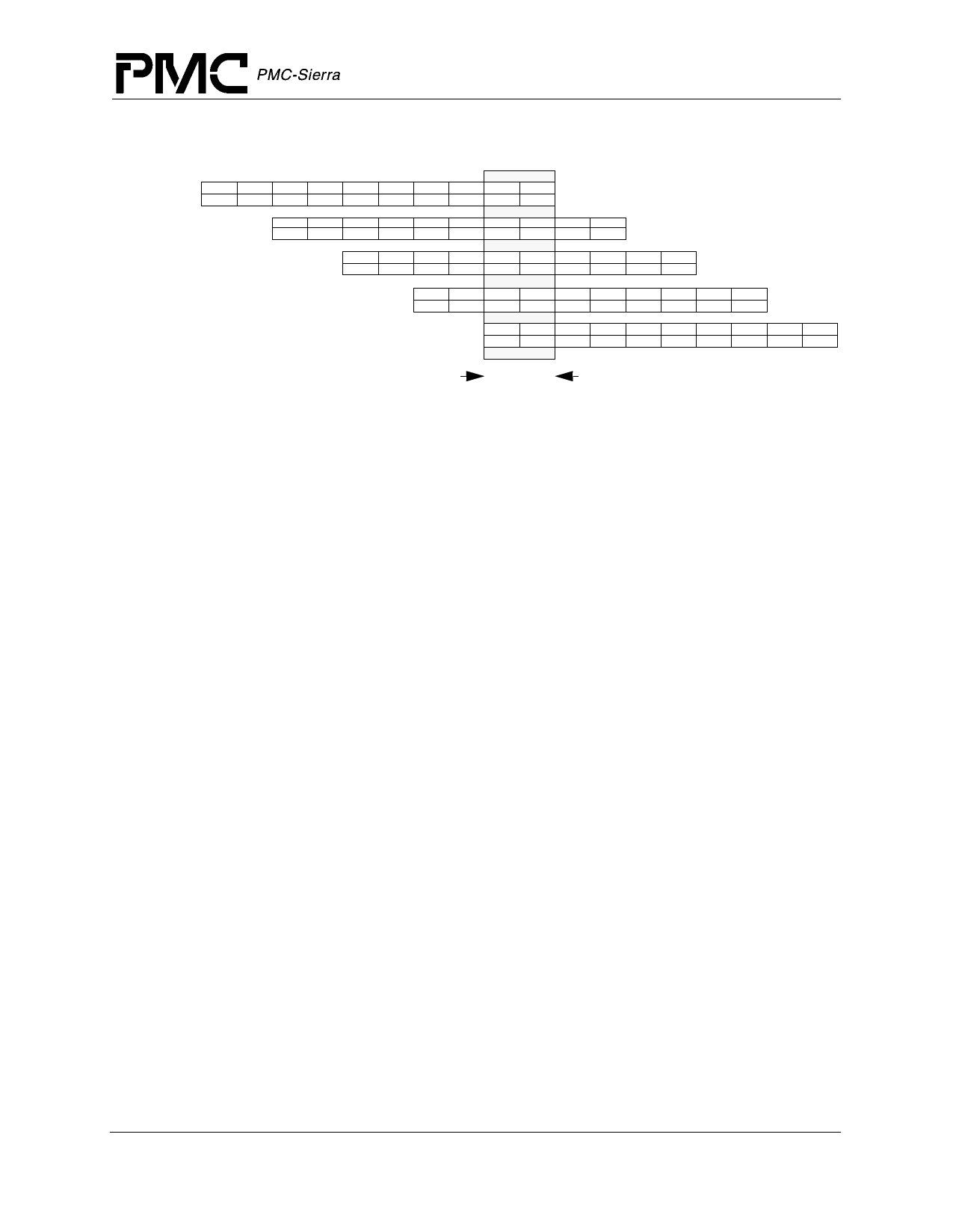

Figure 4 Pipeline

I0 1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I1 1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I2

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I3

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I4

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I5

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I6

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I7

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I8

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

I9

1I 2I 1R 2R 1A 2A 1D 2D 1W 2W

one cycle

1I-1R: Instruction cache access

2I: Instruction virtual to physical address translation

2R: Register file read, Bypass calculation, Instruction decode, Branch address calculation

1A: Issue or slip decision, Branch decision

1A: Data virtual address calculation

1A-2A: Integer add, logical, shift

2A: Store Align

2A-2D: Data cache access and load align

1D: Data virtual to physical address translation

2W: Register file write

Note that instruction dependencies, resource conflicts, and branches result in some of the

instruction slots being occupied by NOPs.

4.4 Integer Unit

Like the RM5200 Fcamily, the RM7000 implements the MIPS IV Instruction Set Architecture,

and is therefore fully upward compatible with applications that run on processors such as the

R4650 and R4700 that implement the earlier generation MIPS III Instruction Set Architecture.

Additionally, the RM7000 includes two implementation specific instructions not found in the

baseline MIPS IV ISA, but that are useful in the embedded market place. Described in detail in a

later section, these instructions are integer multiply-accumulate and three-operand integer

multiply.

The RM7000 integer unit includes thirty-two general purpose 64-bit registers, the HI/LO result

registers for the two-operand integer multiply/divide operations, and the program counter, or PC.

There are two separate execution units, one of which can execute function, or F, type instructions

and one which can execute memory, or M, type instructions. See above for a description of the

instruction types and the issue rules. As a special case, integer multiply/divide instructions as well

as their corresponding MFHI and MFLO instructions can only be executed in the F type

execution unit. Within each execution unit the operational characteristics are the same as on

previous MIPS designs with single cycle ALU operations (add, sub, logical, shift), one cycle load

delay, and an autonomous multiply/divide unit.

Register File

The RM7000 has thirty-two general purpose registers with register location 0 (r0) hard wired to a

zero value. These registers are used for scalar integer operations and address calculation. In order

to service the two integer execution units, the register file has four read ports and two write ports

and is fully bypassed both within and between the two execution units to minimize operation

latency in the pipeline.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

14

Document ID: PMC-2002175, Issue 1