RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

4.11 System Control Coprocessor Registers

The RM7000 incorporates all system control coprocessor (CP0) registers internally. These

registers provide the path through which the virtual memory system’s page mapping is examined

and modified, exceptions are handled, and operating modes are controlled (kernel vs. user mode,

interrupts enabled or disabled, cache features). In addition, the RM7000 includes registers to

implement a real-time cycle counting facility, to aid in cache and system diagnostics, and to assist

in data error detection.

To support the non-blocking caches and enhanced interrupt handling capabilities of the RM7000,

both the data and control register spaces of CP0 are supported by the RM7000. In the data register

space, that is the space accessed using the MFC0 and MTC0 instructions, the RM7000 supports

the same registers as found in the RM5200, R4000 and R5000 families. In the control space, that is

the space accessed by the previously unused CTC0 and CFC0 instructions, the RM7000 supports

five new registers. The first three of these new 32-bit registers support the enhanced interrupt

handling capabilities and are the Interrupt Control, Interrupt Priority Level Lo (IPLLO), and

Interrupt Priority Level Hi (IPLHI) registers. These registers are described further in the section on

interrupt handling. The other two registers, Imprecise Error 1 and Imprecise Error 2, have been

added to help diagnose bus errors which occur on non-blocking memory references.

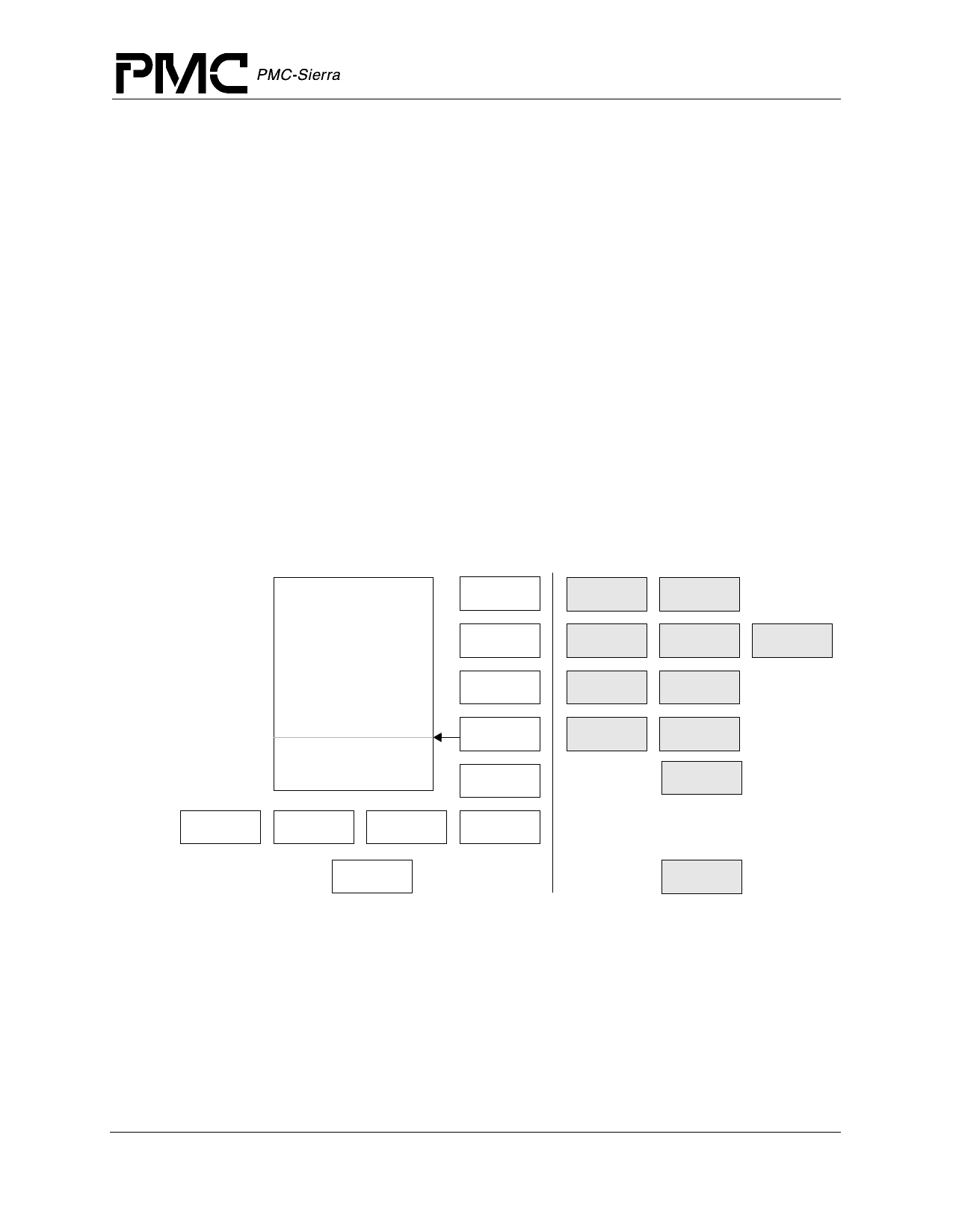

Figure 5 shows the CP0 registers.

Figure 5 CP0 Registers

47

Info

Status

Cause

7*

12*

13*

Index

0*

EPC

14*

Watch1

18*

Watch Mask

24*

TLB

Random

1*

Watch2

19*

XContext

20*

(entries protected

from TLBWR)

0

Wired

6*

PRId

15*

ECC

26*

CacheErr

27*

ErrorEPC

30*

LLAddr

17*

TagLo

28*

TagHi

29*

Config

16*

Used for memory

management

* Register number

Used for exception

processing

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

18

Document ID: PMC-2002175, Issue 1