RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

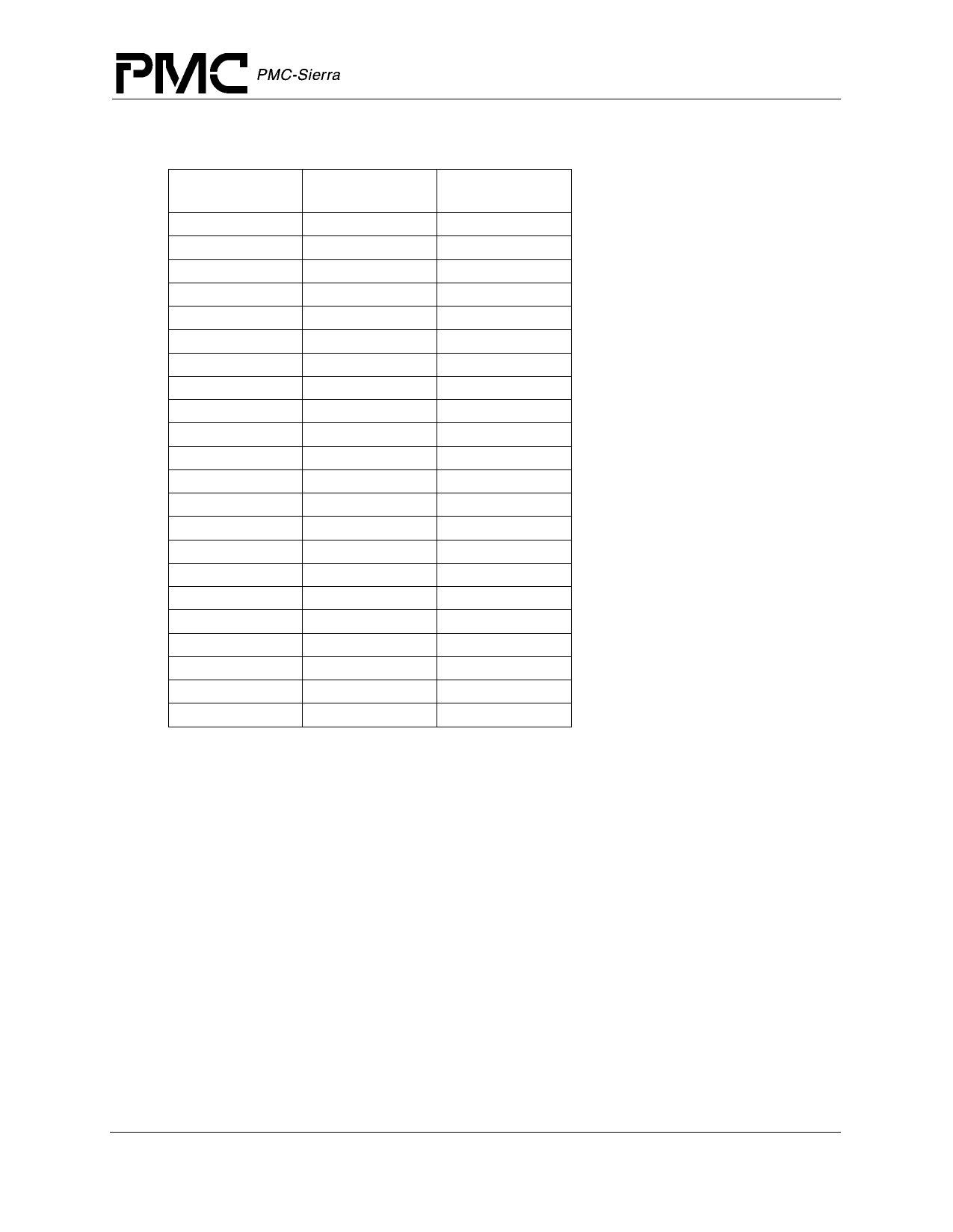

Table 5 Floating Point Latencies and Repeat Rates

Operation

Latency

Single/double

Repeat Rate

Single/double

fadd

4

1

fsub

4

1

fmult

4/5

1/2

fmadd

4/5

1/2

fmsub

4/5

1/2

fdiv

21/36

19/34

fsqrt

21/36

19/34

frecip

21/36

19/34

frsqrt

38/68

36/66

fcvt.s.d

4

1

fcvt.s.w

6

3

fcvt.s.l

6

3

fcvt.d.s

4

1

fcvt.d.w

4

1

fcvt.d.l

4

1

fcvt.w.s

4

1

fcvt.w.d

4

1

fcvt.l.s

4

1

fcvt.l.d

4

1

fcmp

1

1

fmov, fmovc

1

1

fabs, fneg

1

1

To support superscalar operations, the FGR has four read ports and two write ports, and is fully

bypassed to minimize operation latency in the pipeline. Three of the read ports and one write port

are used to support the combined multiply-add instruction while the fourth read and second write

port allows a concurrent floating-point load or store and conditional moves.

4.10 System Control Coprocessor (CP0)

The system control coprocessor (CP0) in the MIPS architecture is responsible for the virtual

memory sub-system, the exception control system, and the diagnostics capability of the processor.

In the MIPS architecture, the system control coprocessor (and thus the kernel software) is

implementation dependent. For memory management, the RM7000 CP0 is logically identical to

that of the RM5200 Family and R5000. For interrupt exceptions and diagnostics, the RM7000 is a

superset of the RM5200 Family and R5000 implementing additional features described later in the

sections on Interrupts, the Test/Breakpoint facility, and the Performance Counter facility.

The memory management unit controls the virtual memory system page mapping. It consists of an

instruction address translation buffer (ITLB), a data address translation buffer (DTLB), a Joint

TLB (JTLB), and coprocessor registers used by the virtual memory mapping sub-system.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

17

Document ID: PMC-2002175, Issue 1