RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

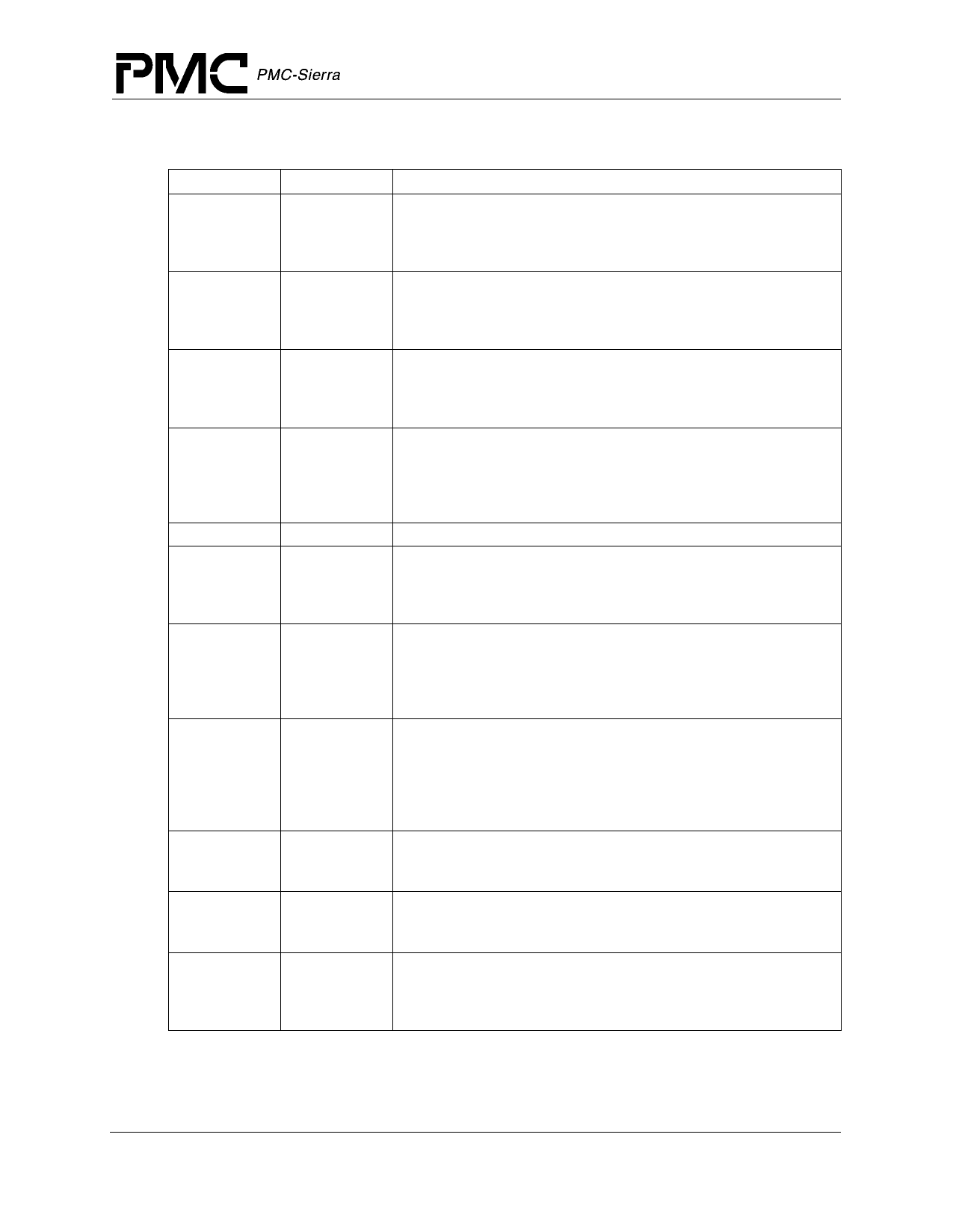

Table 19 Tertiary cache interfacePins

Pin Name Type

Description

TcCLR*

Output

Tertiary Cache Block Clear

Requests that all valid bits be cleared in the Tag RAMs. Many RAM’s

may not support a block clear therefore the block clear capability is not

required for the cache to operate.

TcCWE*(1:0) Output

Tertiary Cache Write Enable

Asserted to cause a write to the cache. Two identical signals are

provided to balance the capacitive load relative to the remaining cache

interface signals.

TcDCE*(1:0) Output

Tertiary Cache Data RAM Chip Enable

When asserted this signal causes the data RAM’s to read out their

contents. Two identical signals are provided to balance the capacitive

load relative to the remaining cache interface signals

TcDOE*

Input

Tertiary Cache Data RAM Output Enable

When asserted this signal causes the data RAM’s to drive data onto

their I/O pins. This signal is monitored by the processor to determine

when to drive the data RAM write enable in a tertiary cache miss refill

sequence.

TcLine(17:0) Output

Tertiary Cache Line Index

TcMatch

Input

Tertiary Cache Tag Match

This signal is asserted by the cache Tag RAM’s when a match occurs

between the value on its data inputs and the contents of the addressed

location in the RAM.

TcTCE*

Output

Tertiary Cache Tag RAM Chip Enable

When asserted this signal will cause either a probe or a write of the Tag

RAM’s depending on the state of the Tag RAM’s write enable signal.

This signal is monitored by the external agent and indicates to it that a

tertiary cache access is occurring.

TcTDE*

Output

Tertiary Cache Tag RAM Data Enable

When asserted this signal causes the value on the data inputs of the

Tag RAM to be latched into the RAM. If a refill of the RAM is necessary,

this latched value will be written into the Tag RAM array. Latching the

Tag allows a shared address/data bus to be used without incurring a

penalty to re-present the Tag during the refill sequence.

TcTOE*

Output

Tertiary Cache Tag RAM Output Enable

When asserted this signal causes the Tag RAM’s to drive data onto

their I/O pins.

TcWord(1:0)

Input/Output

Tertiary Cache Double Word Index

Driven by the processor on cache hits and by the external agent on

cache miss refills.

TcValid

Input/Output

Tertiary Cache Valid

This signal is driven by the processor as appropriate to make a cache

line valid or invalid. On Tag read operations the Tag RAM will drive this

signal to indicate the line state.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

41

Document ID: PMC-2002175, Issue 1