IT66121FN View Datasheet(PDF) - ITE Tech. INC.

Part Name

Description

Manufacturer

IT66121FN Datasheet PDF : 39 Pages

| |||

IT66121FN

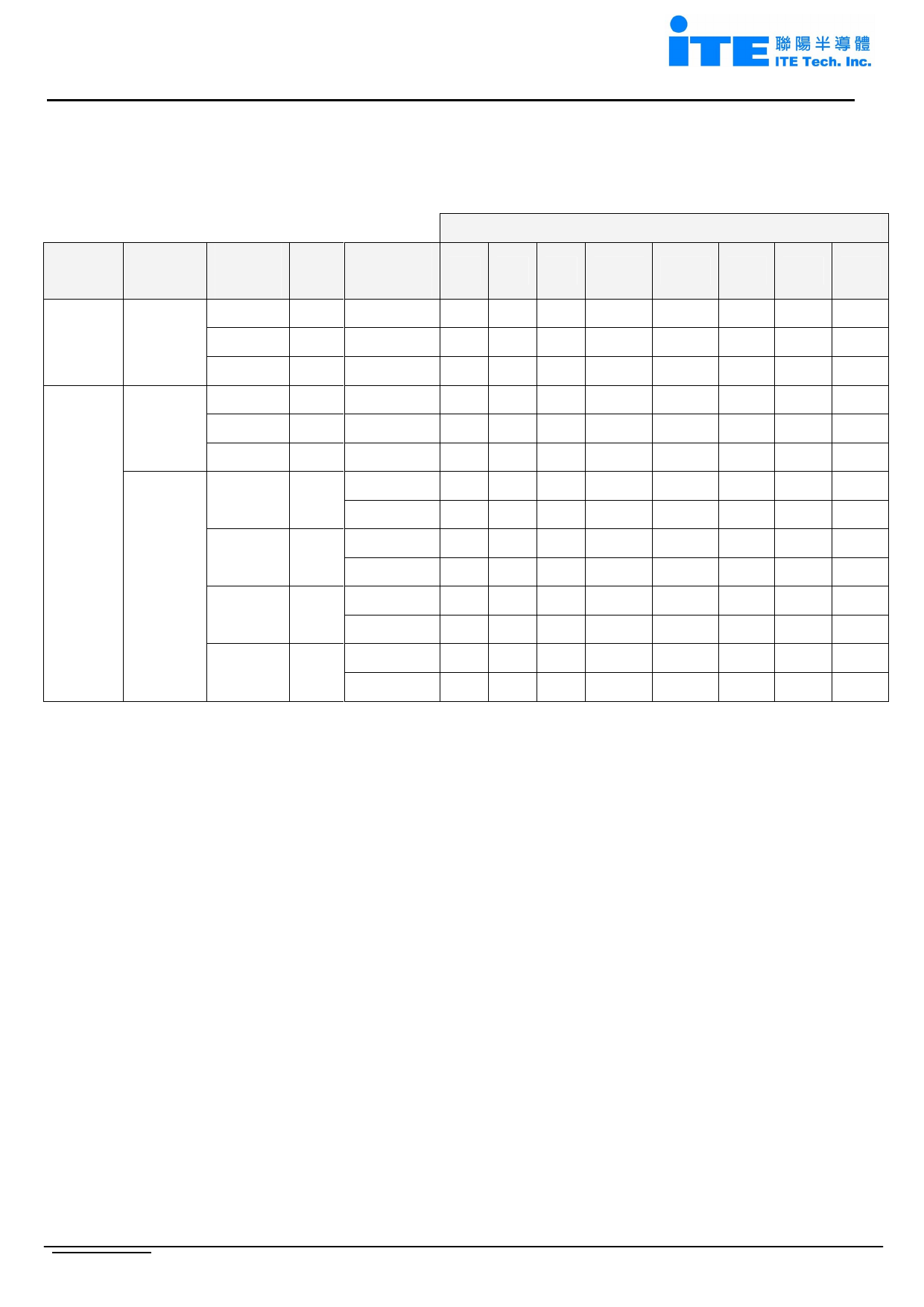

Supported Input Video Formats

Table 1 lists the input video formats supported by IT66121.

Input Pixel clock frequency (MHz)

Color

Space

Video

Format

Bus

Width

DDR/

SDR

Hsync/

Vsync

480i 480p XGA 720p 1080i SXGA 1080p UXGA

24

SDR Separate 13.5 27 65 74.25 74.25 108 148.5 162

RGB

4:4:4

12

DDR Separate 13.5 27 65 74.25 74.25

24

DDR Separate

13.5 32.5 37.125 37.125 54 74.25 81

24

SDR Separate 13.5 27 65 74.25 74.25 108 148.5 162

4:4:4

12

DDR Separate 13.5 27 65 74.25 74.25

24

DDR Separate

13.5 32.5 37.125 37.125 54 74.25 81

Separate 13.5 27 65 74.25 74.25 108 148.5 162

16/20/24 SDR

Embedded 13.5 27 65 74.25 74.25 108 148.5 162

YCbCr

4:2:2

Separate

16/20/24 DDR

Embedded

13.5 32.5 37.125 37.125 54 74.25 81

13.5 32.5 37.125 37.125 54 74.25 81

Separate 27

8/10/12 SDR

Embedded 27

54 130 148.5 148.5

54 130 148.5 148.5

Separate 13.5 27 65 74.25 74.25

8/10/12 DDR

Embedded 13.5 27 65 74.25 74.25

Table 1. Input video formats supported by IT66121

Notes:

1. Table cells that are left blanks are those format combinations that are not supported by IT66121.

2. Embedded sync signals are defined by CCIR-656 standard, using SAV/EAV sequences of FF, 00, 00, XY.

3. The original pixel clock of 480i is 13.5MHz. HDMI standard mandates that a 27MHz pixel clock be used and pixel

repeating is employed to keep the frequency range of the HDMI link within control.

Audio Data Capture and Processing

IT66121 takes in four I2S inputs as well as one S/PDIF input of audio data. The four I2S inputs allow

transmission of 8-channel uncompressed audio data at up to 192kHz sample rate. The S/PDIF input

allows transmission of uncompressed PCM data (IEC 60958) or compressed multi-channel data (IEC

61937) at up to 192kHz.

Note that MCLK input is optional for the IT66121. By default IT66121 generates the MCLK internally to

process the audio. Neither I2S nor S/PDIF inputs requires external MCLK signal. However, if the jitter

or the duty cycle of the input S/PDIF is considerable, coherent external MCLK input is recommended

and such configuration could be enabled through register setting. Refer to IT66121 Programming

Guide for such setting.

www.ite.com.tw

Nov-2011 Rev:0.99 10/39