S25FL127SABMFI003 View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

S25FL127SABMFI003 Datasheet PDF : 142 Pages

| |||

S25FL127S

1.2.2.8

New Features

The FL-S family introduces several new features to SPI category memories:

Extended address for access to higher memory density.

AutoBoot for simpler access to boot code following power up.

Enhanced high performance read commands using mode bits to eliminate the overhead of SIO instructions when repeating

the same type of read command.

Multiple options for initial read latency (number of dummy cycles) for faster initial access time or higher clock rate read

commands.

Automatic ECC for enhanced data integrity.

Advanced Sector Protection for individually controlling the protection of each sector. This is very similar to the Advanced

Sector Protection feature found in several other Cypress parallel interface NOR memory families.

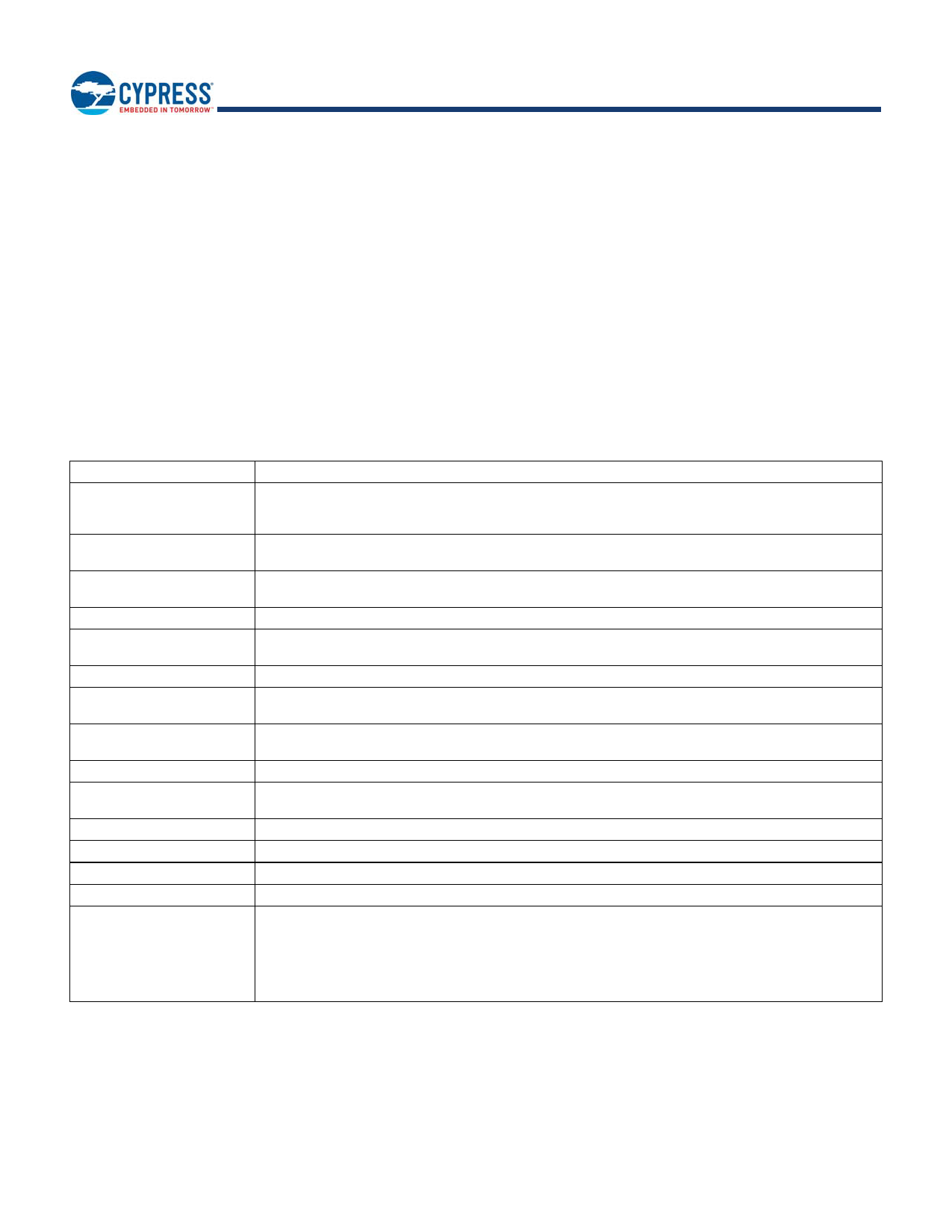

1.3 Glossary

BCD

Command

ECC

Flash

High

Instruction

Low

LSB

(Least Significant Bit)

MSB

(Most Significant Bit)

Non-Volatile

OPN

(Ordering Part Number)

Page

PCB

Register Bit References

Sector

Write

Binary Coded Decimal. A Value in which each 4-bit nibble represents a decimal numeral.

All information transferred between the host system and memory during one period while CS# is low. This

includes the instruction (sometimes called an operation code or opcode) and any required address, mode bits,

latency cycles, or data.

ECC Unit = 16 byte aligned and length data groups in the main Flash array and OTP array, each of which has its

own hidden ECC syndrome to enable error correction on each group.

The name for a type of Electrical Erase Programmable Read Only Memory (EEPROM) that erases large blocks

of memory bits in parallel, making the erase operation much faster than early EEPROM.

A signal voltage level ≥ VIH or a logic level representing a binary one (1).

The 8-bit code indicating the function to be performed by a command (sometimes called an operation code or

opcode). The instruction is always the first 8 bits transferred from host system to the memory in any command.

≤ A signal voltage level VIL or a logic level representing a binary zero (0).

Generally the right most bit, with the lowest order of magnitude value, within a group of bits of a register or data

value.

Generally the left most bit, with the highest order of magnitude value, within a group of bits of a register or data

value.

No power is needed to maintain data stored in the memory.

The alphanumeric string specifying the memory device type, density, package, factory non-volatile configuration,

etc. used to select the desired device.

512 bytes or 256 bytes aligned and length group of data.

Printed Circuit Board

Are in the format: Register_name[bit_number] or Register_name[bit_range_MSB: bit_range_LSB]

Erase unit size; depending on device model and sector location this may be 4 kbytes, 64 kbytes or 256 kbytes.

An operation that changes data within volatile or non-volatile registers bits or non-volatile flash memory. When

changing non-volatile data, an erase and reprogramming of any unchanged non-volatile data is done, as part of

the operation, such that the non-volatile data is modified by the write operation, in the same way that volatile data

is modified – as a single operation. The non-volatile data appears to the host system to be updated by the single

write command, without the need for separate commands for erase and reprogram of adjacent, but unaffected

data.

Document Number: 001-98282 Rev. *I

Page 7 of 142