IDT79R4650-100DP(2000) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-100DP

(Rev.:2000)

(Rev.:2000)

IDT79R4650-100DP Datasheet PDF : 25 Pages

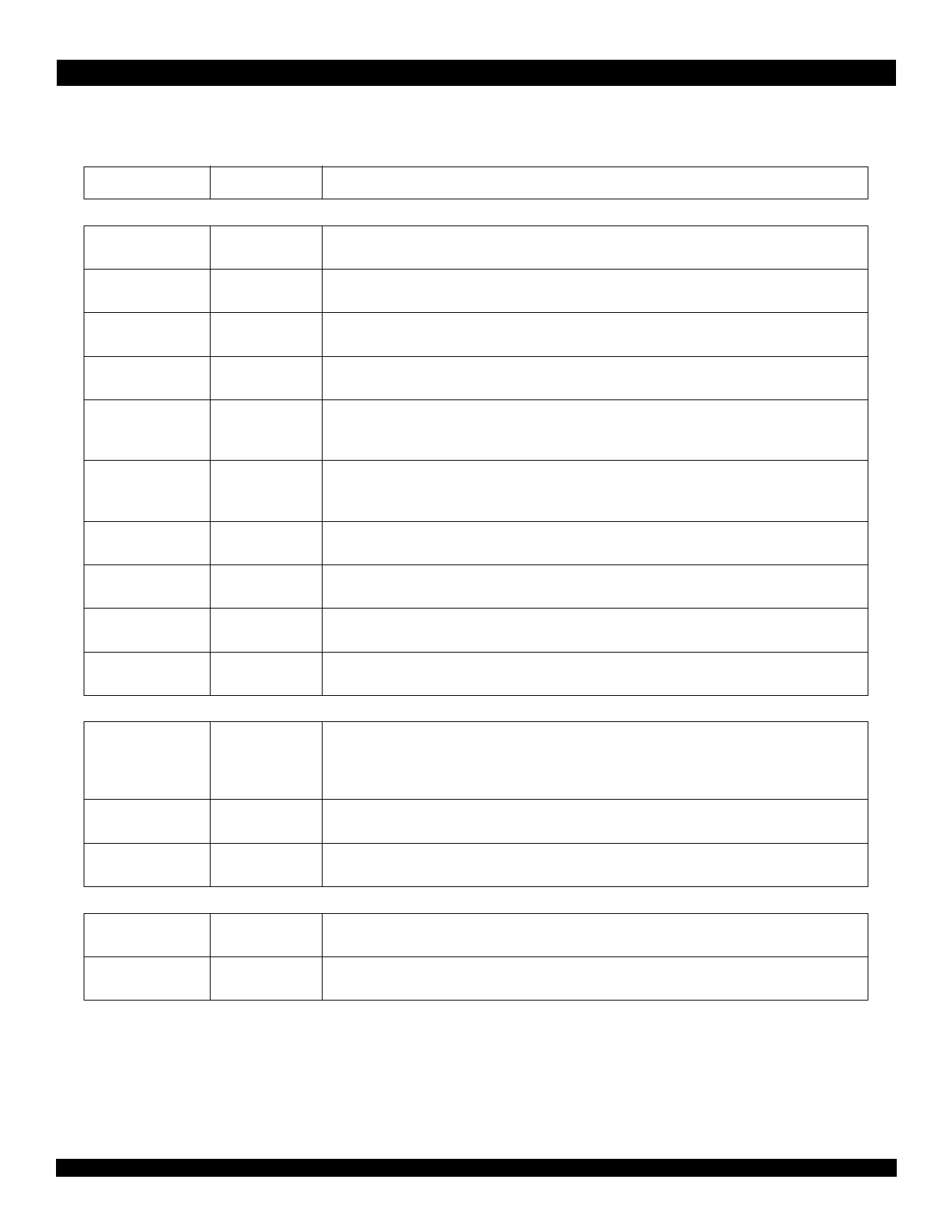

| |||

IDT79RC4650™

3LQ#'HVFULSWLRQV

The following is a list of interface, interrupt, and miscellaneous pins available on the RC4650. Pins marked with one asterisk are active when low.

####3LQ#1DPH

System interface:

ExtRqst*

7\SH

Input

Release*

Output

RdRdy*

Input

WrRdy*

Input

ValidIn*

Input

ValidOut*

Output

SysAD(63:0)

Input/Output

SysADC(7:0)

Input/Output

SysCmd(8:0)

Input/Output

SysCmdP

Input/Output

Clock/control interface:

MasterClock

Input

VCCP

Input

VSSP

Input

Interrupt interface:

Int*(5:0)

Input

NMI*

Input

'HVFULSWLRQ

External request

Signals that the system interface needs to submit an external request.

Release interface

Signals that the processor is releasing the system interface to slave state

Read Ready

Signals that an external agent can now accept a processor read.

Write Ready

Signals that an external agent can now accept a processor write request.

Valid Input

Signals that an external agent is now driving a valid address or data on the SysAD bus and a valid com-

mand or data identifier on the SysCmd bus.

Valid output

Signals that the processor is now driving a valid address or data on the SysAD bus and a valid command

or data identifier on the SysCmd bus.

System address/data bus

A 64-bit address and data bus for communication between the processor and an external agent.

System address/data check bus

An 8-bit bus containing parity check bits for the SysAD bus during data bus cycles.

System command/data identifier bus

A 9-bit bus for command and data identifier transmission between the processor and an external agent.

Reserved system command/data identifier bus parity

For the RC4650 this signal is unused on input and zero on output.

Master clock

Master clock input used as the system interface reference clock. All output timings are relative to this input

clock. Pipeline operation frequency is derived by multiplying this clock up by the factor selected during

boot initialization.

Quiet VCC for PLL

Quiet VCC for the internal phase locked loop.

Quiet VSS for PLL

Quiet VSS for the internal phase locked loop.

Interrupt

Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt register.

Non-maskable interrupt

Non-maskable interrupt, ORed with bit 6 of the interrupt register.

11 of 25

March 28, 2000