CDP1805AC View Datasheet(PDF) - Intersil

Part Name

Description

Manufacturer

CDP1805AC Datasheet PDF : 30 Pages

| |||

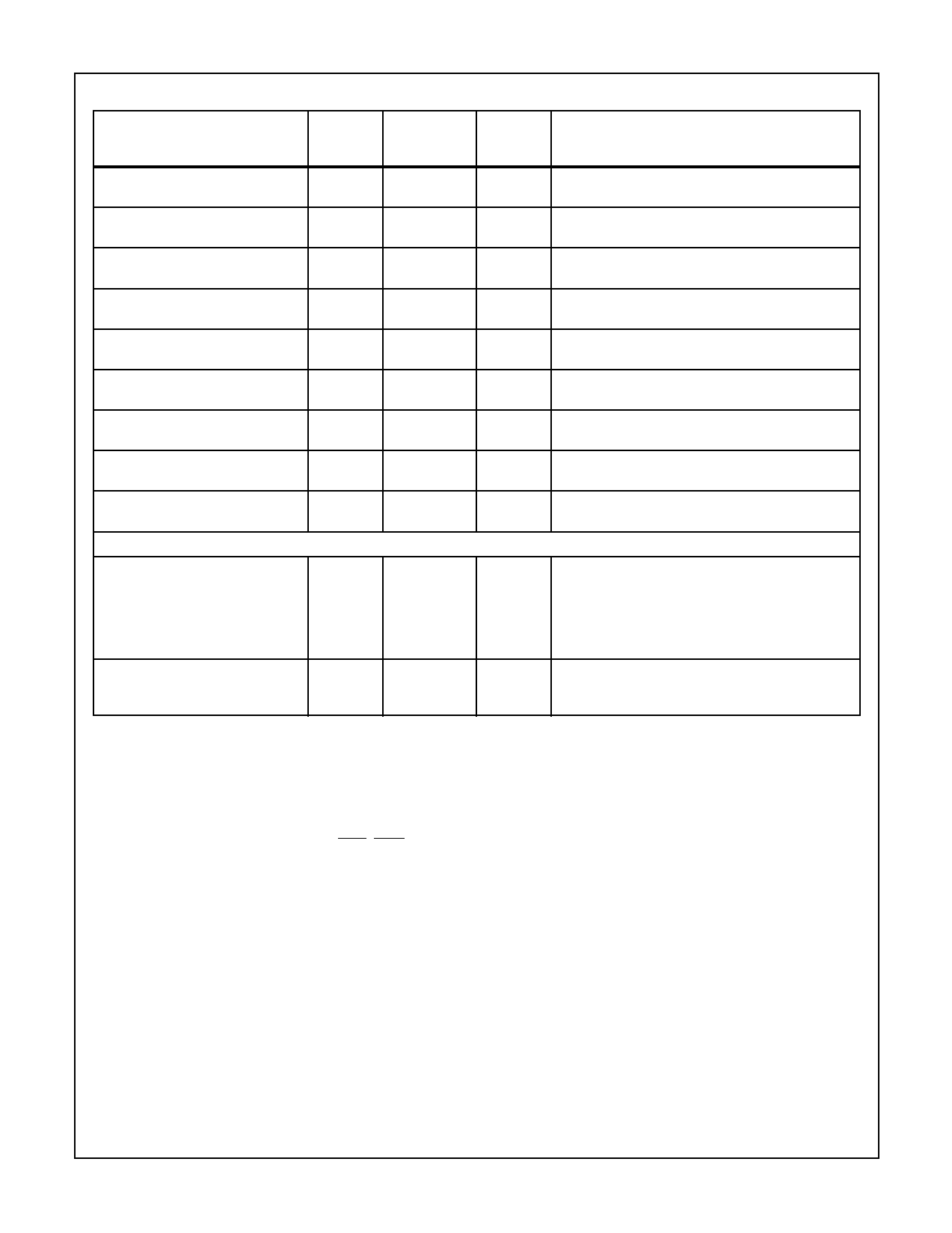

CDP1805AC, CDP1806AC

INSTRUCTION

OUTPUT 6

OUTPUT 7

INPUT 1

INPUT 2

INPUT 3

INPUT 4

INPUT 5

INPUT 6

INPUT 7

CALL AND RETURN

STANDARD CALL

STANDARD RETURN

TABLE 1. INSTRUCTION SUMMARY (SEE NOTES) (Continued)

NO. OF

MACHINE

CYCLES

MNEMONIC

OP CODE

OPERATION

2

OUT 6

66

M(R(X)) → BUS; R(X) + 1 → R(X)

N LINES = 6

2

OUT 7

67

M(R(X)) → BUS; R(X) + 1 → R(X)

N LINES = 7

2

INP 1

69

BUS → M(R(X)); BUS → D

N LINES = 1

2

INP 2

6A

BUS → M(R(X)); BUS → D

N LINES = 2

2

INP 3

6B

BUS → M(R(X)); BUS → D

N LINES = 3

2

INP 4

6C

BUS → M(R(X)); BUS → D

N LINES = 4

2

INP 5

6D

BUS → M(R(X)); BUS → D

N LINES = 5

2

INP 6

6E

BUS → M(R(X)); BUS → D

N LINES = 6

2

INP 7

6F

BUS → M(R(X)); BUS → D

N LINES = 7

10

SCAL

688N R(N).0 → M(R(X));

(Note 10) R(N).1 → M(R(X) - 1);

R(X) - 2 → R(X); R(P) → R(N);

THEN M(R(N)) → R(P).1;

M(R(N) + 1) → R(P).0;

R(N) + 2 → R(N)

8

SRET

689N R(N) → R(P);

(Note 10) M(R(X) + 1) → R(N).1;

M(R(X) + 2) → R(N).0; R(X) + 2 → R(X)

NOTES:

10. Previous contents of T register are destroyed during instruction execution.

11. This instruction is associated with more than one mnemonic. Each mnemonic is individually listed.

12. ETQ cleared by LDC with the Counter/Timer stopped, reset of CPU, or BCl • (Cl = 1).

13. Cl = Counter Interrupt, Xl = External Interrupt.

14. An IDLE instruction initiates an S1 cycle. All external signals, except the oscillator, are stopped on the low-to-high transition of TPB. All

outputs remain in their previous states, MRD, MWR, are set to a logic ‘1’ and the data bus floats. The processor will continue to IDLE

until an I/O request (INTERRUPT, DMA-IN, or DMA-OUT) is activated. When the request is acknowledged, the IDLE cycle is terminated

and the I/O request is serviced, and the normal operation is resumed. (To respond to an lNTERRUPT during an IDLE, MlE and either

ClE or XlE must be enabled).

15. Long-Branch, Long-Skip and No Op instructions require three cycles to complete (1 fetch + 2 execute).

Long-Branch instructions are three bytes long. The first byte specifies the condition to be tested; and the second and third byte, the

branching address.

The long branch instruction can:

a. Branch unconditionally

b. Test for D = 0 or D ≠ 0

c. Test for DF = 0 or DF = 1

d. Test for Q = 0 or Q = 1

e. Effect an unconditional no branch

If the tested condition is met, then branching takes place; the branching address bytes are loaded in the high-and-low-order bytes of the

current program counter, respectively. This operation effects a branch to any memory location.

If the tested condition is not met, the branching address bytes are skipped over, and the next instruction in sequence is fetched and exe-

cuted. This operation is taken for the case of unconditional no branch (NLBR).

22