SPHE8200A View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

SPHE8200A Datasheet PDF : 40 Pages

| |||

Preliminary

SPHE8200A

Video contrast/bright/color enhancement

Picture

control

Q matrix

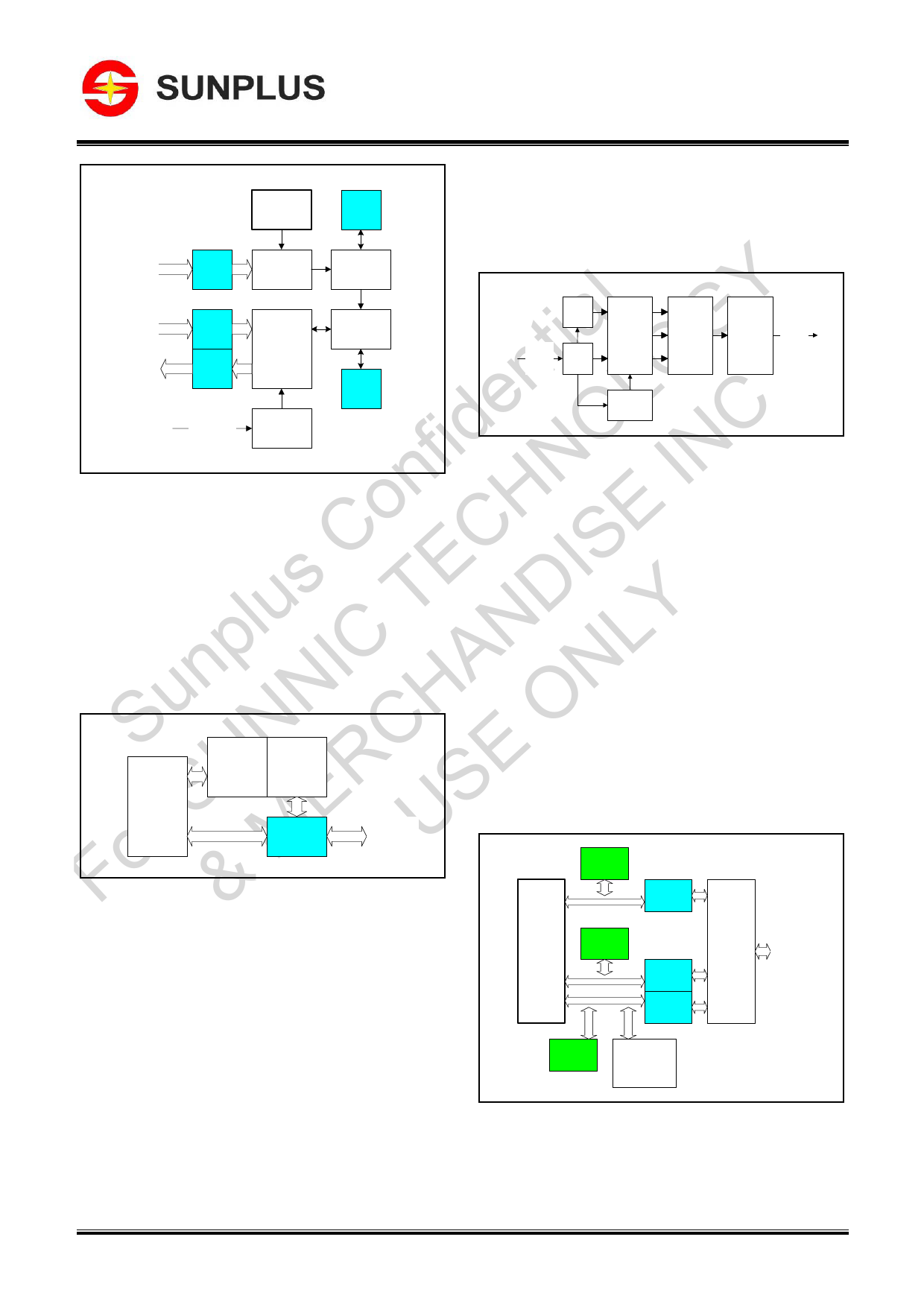

During runtime video post-processing hardware will fetch video

sources from framebuffer and process the data as in the following

figure.

l Y Memory

fidentiaOLOGC Interface

input

FIFO

Variable

length

decoder

Inverse

quantization

input

buffer

output

buffer

Motion

compensation

display

information

Decoding

control

Inverse DCT

DCT

buffer

n N IN Figure 5-8: architecture of video decoding pipeline

o H E 5.10. Graphics Engine BondyPro®

C C For thin-client or set-top box applications, 2D graphics capabilities

s E IS are key to system performance. This graphics engine is able to

perform fast BitBlt and 2D drawing functions. The graphics engine

lu T D is combined with 2 parts: graphics command interpreter and

Y graphics datapath. Upon receiving command from RISC,

np IC N L interpreter will send micro-commands to graphics datapath, where

A N raster operations are executed.

line

buffer

from

memory

interface

input

buffer

de-interlac

Vertical

filtering

cdhrom a

resampl

de-interlac

buffer

CIF and

horizonta

expansio

to

display

interface

5.12. Audio DSP

The SPHE8200 contains a high-performance 24-bit audio DSP

optimized for embedded systems. The DSP processor can fetch

operands

from

memories

and

perform

multiplication-and-accumulation (MAC) in one cycle. During

execution the DSP fetches instruction from main-memory or IROM,

at the same time the ICACHE will store the LRU instructions.

Data are loaded from and to main-memory by using the

cycle-stealing DMA channels. There are 3 independent

cycle-stealing DMA channels that allow DSP run without stalled by

memory access.

SuSUNNERCHSE O RISC

r U subsyste

Grap

comma

interpret

Grap

data

Graph

work

Memo

Interfa

Fo & M Figure 5-9: BondyPro® architecture

The DSP works closely with RISC processors by using mailbox

registers or shared-memory protocol. When downloaded with

different codec firmware the DSP could support multi-standard

audio and act as an accelerator for RISC in some case.

IROM

ICACHE

5.11. Video Post Processing

SPHE8200 includes powerful video-post-processing facilities to

provide high video quality. It perform following functions:

YUV411, YUV420, YUV422 and 8-bit indexed color

SIF to CCIR601 interpolation

MPEG1 CIF filter

MPEG1/2 chroma vertical interpolation

Up to 1/2x horizontal decimation

Up to 1/512x vertical decimation

Up to 1024x horizontal expansion

Up to 1024x vertical expansion

Powerful de-interlacing hardware

Pan and scan function

De-flicker during interlaced display

data

DSP

ROM

BIU

Memory

interface

data

RAM

data

RAM

data

audio

ROM

interface

controller

Figure 5-10: Audio DSP architecture

© Sunplus Technology Co., Ltd.

21

Proprietary & Confidential

OCT. 07, 2003

Preliminary Version: 0.2