SPHE8200A View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

SPHE8200A Datasheet PDF : 40 Pages

| |||

Preliminary

SPHE8200A

BCK

012

22 23 24

31 0 1 2

31 0

LRCK

left channel

l Y AUDATA[]

23 22 21

MSB

10

LSB

right channel

23 22 21

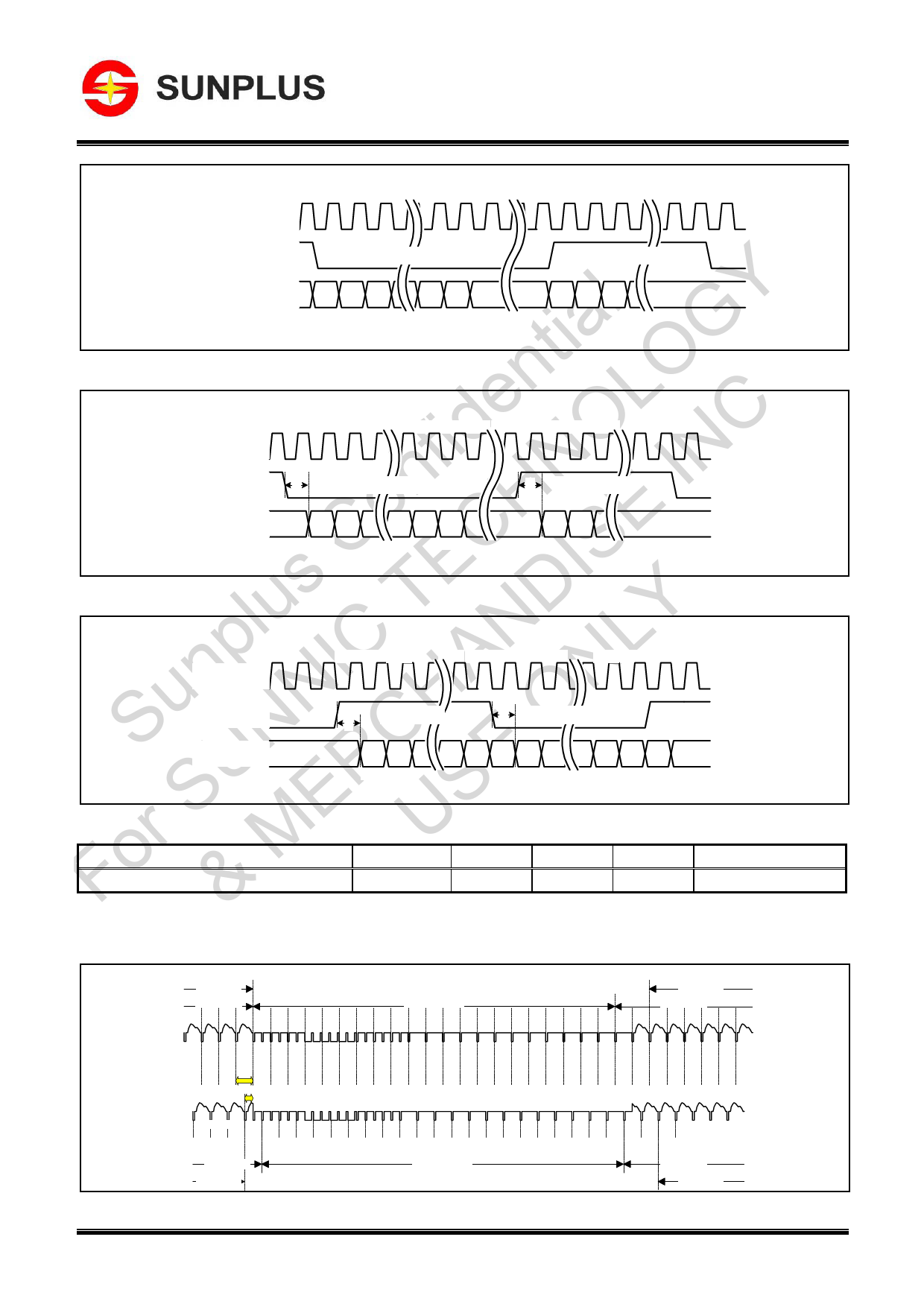

tia G Figure 6-5: Left justified mode / 24bit data / 32bit frame / MSB first

fiden OLO C BCK

n N IN LRCK

o H E AUDATA[]

0123

23 24 25 31 0 1 2 3

D

left channel

23 22 21 2

MSB

10

LSB

D

right channel

23 22

31 0

s C EC IS Figure 6-6: I2S mode / 24bit data / 32bit frame

nplu IC T AND LY BCK

u N H N LRCK

S SUN ERC SE O AUDATA[]

012

22 23 0 1 2

22 23 0 1

left channel

D

D

right channel

23 22 21 2 1 0 23 22 21 2 1 0

MSB

LSB MSB

LSB

Figure 6-7: I2S mode / 24bit data / 24bit frame

or M U Parameter

Symbol

Min

Typ

Max

Units

F & BCK rising to LRCK / AUDATA transition

tS

-

0.5

-

System clock cycle

6.4.4. Video timing diagrams

Interlaced Modes

SP active period

active line period

V blanking period (21)

SP active period

active line period

Video line number

522 523 524 525 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

SP line number

473 475 477 479

0 2 4 6 8 10 12

Video line number

260 261 262 263 264 265 266 267 268 269 270 271 272 273 274 275 276 277 278 279 280 281 282 283 284 285 286 287 288 289 290 291

SP line number

474 476 478

1 3 5 7 9 11

active line period

V blanking period (21)

active line period

SP active period

SP active period

Figure 6-8: NTSC (480i) timing diagram

© Sunplus Technology Co., Ltd.

28

Proprietary & Confidential

OCT. 07, 2003

Preliminary Version: 0.2