TC7136 View Datasheet(PDF) - Microchip Technology

Part Name

Description

Manufacturer

TC7136 Datasheet PDF : 22 Pages

| |||

TC7136/TC7136A

4.0 ANALOG SECTION

In addition to the basic integrate and de-integrate dual

slope cycles discussed above, the TC7136 and

TC7136A designs incorporate an "integrator output

zero cycle" and an "auto-zero cycle." These additional

cycles ensure the integrator starts at 0V (even after a

severe over range conversion) and that all offset volt-

age errors (buffer amplifier, integrator and comparator)

are removed from the conversion. A true digital zero

reading is assured without any external adjustments.

A complete conversion consists of four distinct phases:

1. Integrator output zero phase

2. Auto-zero phase

3. Signal integrate phase

4. Reference de-integrate phase

4.1 Integrator Output Zero Phase

This phase ensures the integrator output is at 0V

before the system zero phase is entered. This ensures

that true system offset voltages will be compensated

for, even after an over range conversion. The count for

this phase is a function of the number of counts

required by the de-integrate phase. The count lasts

from 11 to 140 counts for non over range conversions

and from 31 to 640 counts for over range conversions.

4.2 Auto-Zero Phase

During the auto-zero phase, the differential input signal

is disconnected from the circuit by opening internal

analog gates. The internal nodes are shorted to analog

common (ground) to establish a zero input condition.

Additional analog gates close a feedback loop around

the integrator and comparator. This loop permits com-

parator offset voltage error compensation. The voltage

level established on CAZ compensates for device offset

voltages. The auto-zero phase residual is typically

10μV to 15μV.

The auto-zero duration is from 910 to 2900 counts for

non over range conversions and from 300 to 910

counts for over range conversions.

4.3 Signal Integration Phase

The auto-zero loop is entered and the internal differen-

tial inputs connect to VIN+ and VIN-. The differential

input signal is integrated for a fixed time period. The

TC7136/A signal integration period is 1000 clock peri-

ods or counts. The externally set clock frequency is

divided by four before clocking the internal counters.

The integration time period is:

EQUATION 4-1:

tSI =

4

FOSC

x 1000

Where FOSC = external clock frequency.

The differential input voltage must be within the device

Common mode range when the converter and mea-

sured system share the same power supply common

(ground). If the converter and measured system do not

share the same power supply common, VIN- should be

tied to analog common.

Polarity is determined at the end of signal integrate

phase. The sign bit is a true polarity indication, in that

signals less than 1LSB are correctly determined. This

allows precision null detection, limited only by device

noise and auto-zero residual offsets.

4.4 Reference Integrate Phase

The third phase is reference integrate or de-integrate.

VIN- is internally connected to analog common and

VIN+ is connected across the previously charged refer-

ence capacitor. Circuitry within the chip ensures that

the capacitor will be connected with the correct polarity

to cause the integrator output to return to zero. The

time required for the output to return to zero is propor-

tional to the input signal and is between 0 and 2000

internal clock periods. The digital reading displayed is:

EQUATION 4-2:

1000 = ----V----I--N------

VREF

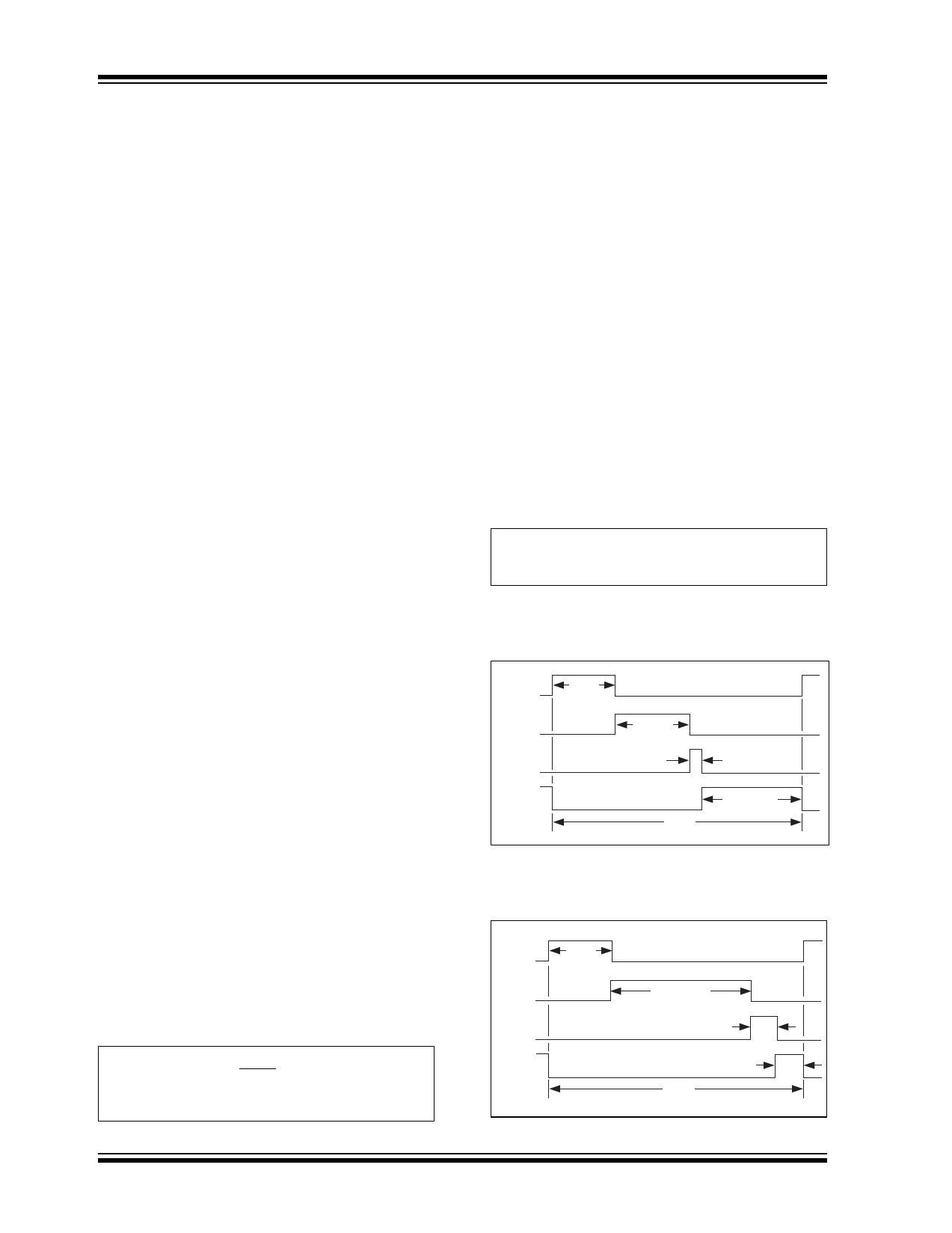

FIGURE 4-1:

INT

DENT

ZI

AZ

1000

CONVERSION TIMING

DURING NORMAL

OPERATION

1-2000

11-140

4000

910-2900

FIGURE 4-2:

INT

DEINT

ZI

AZ

1000

CONVERSION TIMING

DURING OVER RANGE

OPERATION

2001-2090

31-640

4000

300-910

DS21461C-page 10

© 2005 Microchip Technology Inc.