RM7065A-350T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7065A-350T Datasheet PDF : 52 Pages

| |||

RM7065A™ Microprocessor with On-Chip Secondary Cache Data Sheet

Preliminary

4.5 ALU

The RM7065A has two complete integer ALUs each consisting of an integer adder/subtractor, a

logic unit, and a shifter. Table 3 shows the functions performed by the ALUs for each execution

unit. Each of these units is optimized to perform all operations in a single processor cycle.

Table 3 ALU Operations

Unit

F Pipe

M Pipe

Adder

add, sub

add, sub, data address

add

Logic

logic, moves, zero shifts logic, moves, zero shifts

(nop)

(nop)

Shifter

non zero shift

non zero shift, store

align

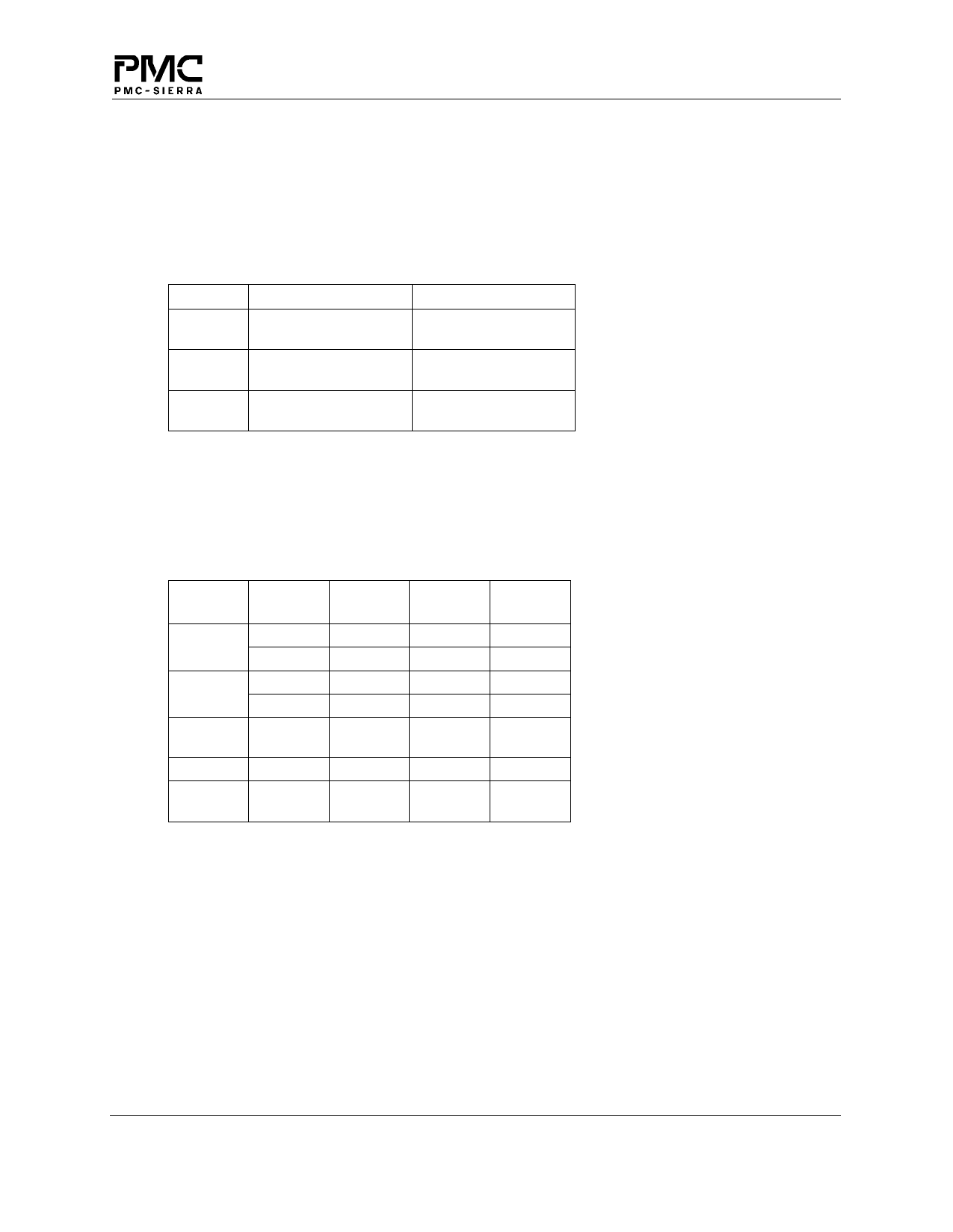

4.6 Integer Multiply/Divide

The RM7065A has a single dedicated integer multiply/divide unit optimized for high-speed

multiply and multiply-accumulate operations. The multiply/divide unit resides in the F type

execution unit. Table 4 shows the performance of the multiply/divide unit on each operation.

Table 4 Integer Multiply/Divide Operations

Operand

Repeat Stall

Opcode Size

Latency Rate

Cycles

MULT/U,

16 bit

4

3

0

MAD/U

32 bit

5

4

0

16 bit

4

3

2

MUL

32 bit

5

4

3

DMULT,

any

9

8

0

DMULTU

DIV, DIVD

any

36

36

0

DDIV,

any

68

68

0

DDIVU

The baseline MIPS IV ISA specifies that the results of a multiply or divide operation be placed in

the Hi and Lo registers. These values can then be transferred to the general purpose register file

using the Move-from-Hi and Move-from-Lo (MFHI/MFLO) instructions.

In addition to the baseline MIPS IV integer multiply instructions, the RM7065A also implements

the 3-operand multiply instruction, MUL. This instruction specifies that the multiply result go

directly to the integer register file rather than the Lo register. The portion of the multiply that

would have normally gone into the Hi register is discarded. For applications where it is known that

the upper half of the multiply result is not required, using the MUL instruction eliminates the

necessity of executing an explicit MFLO instruction.

The multiply-add instructions, MAD and MADU, multiply two operands and add the resulting

product to the current contents of the Hi and Lo registers. The multiply-accumulate operation is

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

15

Document ID: PMC-2010145, Issue 2