RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

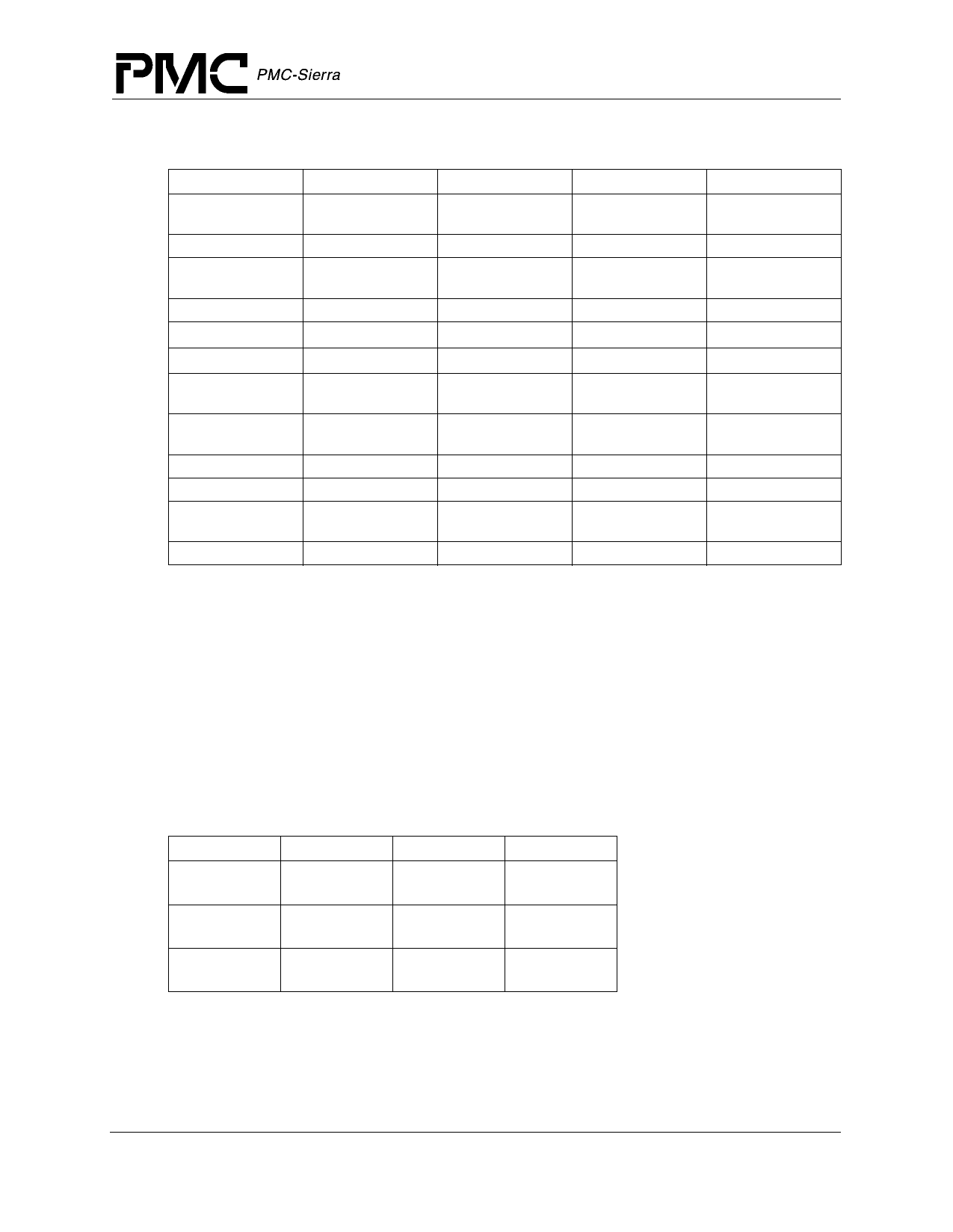

Table 6 Cache Attributes

Attribute

Instruction

Size

16KB

Associativity

Replacement

Algorithm.

Line size

Index

Tag

Write policy

4-way

cyclic

32 byte

vAddr11..0

pAddr35..12

n.a.

read policy

n.a.

read order

write order

miss restart

following:

Parity

critical word first

NA

complete line

per word

Data

16KB

4-way

cyclic

Secondary

256KB

4-way

cyclic

Tertiary

512K, 1M, 2M, 4M,

or 8M

direct mapped

direct replacement

32 byte

vAddr11..0

pAddr35..12

write-back, write-

through

non-blocking (2

outstanding)

critical word first

sequential

first double (if

waiting for data)

per byte

32 byte

32 byte

pAddr15..0

pAddr22..0

pAddr35..16

pAddr35..19

block write-back,

bypass

block write-through,

bypass

non-blocking (data non-blocking (data

only, 2 outstanding) only, 2 outstanding)

critical word first critical word first

sequential

sequential

n.a.

n.a.

per doubleword

per byte

4.22 Cache Locking

The RM7000 allows critical code or data fragments to be locked into the primary and secondary

caches. The user has complete control over what locking is performed with cache line granularity.

For instruction and data fragments in the primaries, locking is accomplished by setting either or

both of the cache lock enable bits in the CP0 ECC register, specifying the set via a field in the CP0

ECC register, and then executing either a load instruction or a Fill_I cache operation for data or

instructions respectively. Only two sets are lockable within each cache: set A and set B. Locking

within the secondary works identically to the primaries using a separate secondary lock enable bit

and the same set selection field. As with the primaries, only two sets are lockable: sets A and B.

Table 7 summarizes the cache locking capabilities.

Table 7 Cache Locking Control

Cache

Lock Enable Set Select

Primary I

ECC[27]

ECC[28]=0→A

ECC[28]=1→B

Primary D

ECC[26]

ECC[28]=0→A

ECC[28]=1→B

Secondary

ECC[25]

ECC[28]=0→A

ECC[28]=1→B

Activate

Fill_I

Load/Store

Fill_I or

Load/Store

4.23 Cache Management

To improve the performance of critical data movement operations in the embedded environment,

the RM7000 significantly improves the speed of operation of certain critical cache management

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

26

Document ID: PMC-2002175, Issue 1