RM7000-250T View Datasheet(PDF) - PMC-Sierra

Part Name

Description

Manufacturer

RM7000-250T Datasheet PDF : 54 Pages

| |||

RM7000™ Microprocessor with On-Chip Secondary Cache Datasheet

Released

operations vis-a-vis the R5000 and R4000 families. In particular, the speed of the Hit-Writeback-

Invalidate and Hit-Invalidate cache operations has been improved in some cases by an order of

magnitude over that of the earlier families. Table 8 compares the RM7000 with the R4000 and

R5000 processors.

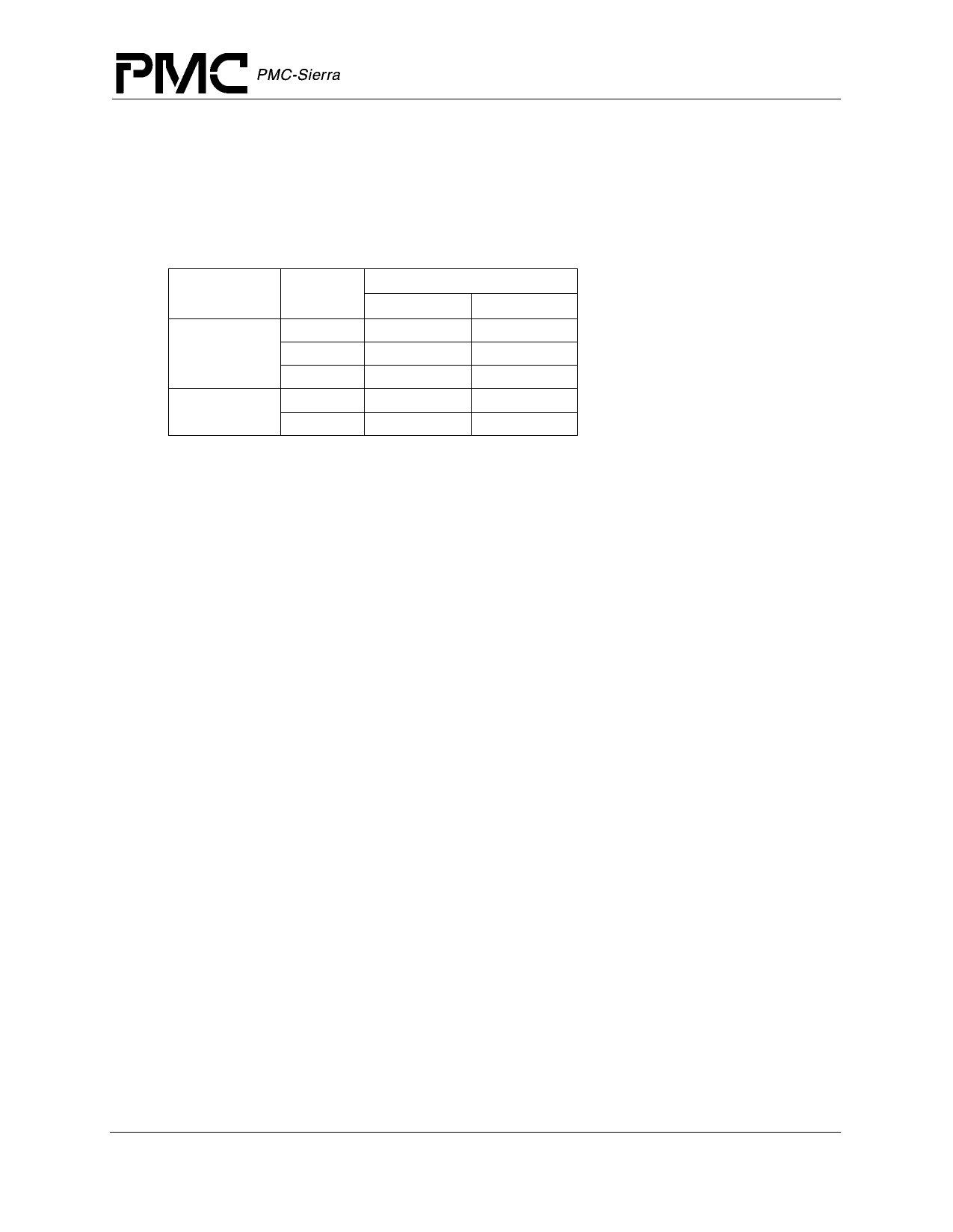

Table 8 Penalty Cycles

Penalty

Operation Condition RM7000

Hit-Writeback- Miss

0

Invalidate

Hit-Clean 3

Hit-Dirty 3+n

Hit-Invalidate Miss

0

Hit

2

R4000/R5000

7

12

14+n

7

9

For the Hit-Dirty case of Hit-Writeback-Invalidate, if the writeback buffer is full from some

previous cache eviction then n is the number of cycles required to empty the writeback buffer. If

the buffer is empty then n is zero.

The penalty value is the number of processor cycles beyond the one cycle required to issue the

instruction that is required to implement the operation.

4.24 Primary Write Buffer

Writes to secondary cache or external memory, whether cache miss write-backs or stores to

uncached or write-through addresses, use the integrated primary write buffer. The write buffer

holds up to four 64-bit address and data pairs. The entire buffer is used for a data cache write-back

and allows the processor to proceed in parallel with memory update. For uncached and write-

through stores, the write buffer significantly increases performance by decoupling the SysAD bus

transfers from the instruction execution stream.

4.25 System Interface

The RM7000 provides a high-performance 64-bit system interface which is compatible with the

RM5200 Family and R5000. Unlike the R4000 and R5000 family processors which provide only

an integral multiplication factor between SysClock and the pipeline clock, the RM7000 also

allows half-integral multipliers, thereby providing greater granularity in the designers choice of

pipeline and system interface frequencies.

The interface consists of a 64-bit Address/Data bus with 8 check bits and a 9-bit command bus. In

addition, there are ten handshake signals and ten interrupt inputs. The interface has a simple timing

specification and is capable of transferring data between the processor and memory at a peak rate

of 1000 MB/sec with a 125 MHz SysClock.

Figure 8 shows a typical embedded system using the RM7000. This example shows a system with

a bank of DRAMs, an optional tertiary cache, and an interface ASIC which provides DRAM

control as well as an I/O port.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

27

Document ID: PMC-2002175, Issue 1