MPC2605ZP66R View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MPC2605ZP66R Datasheet PDF : 30 Pages

| |||

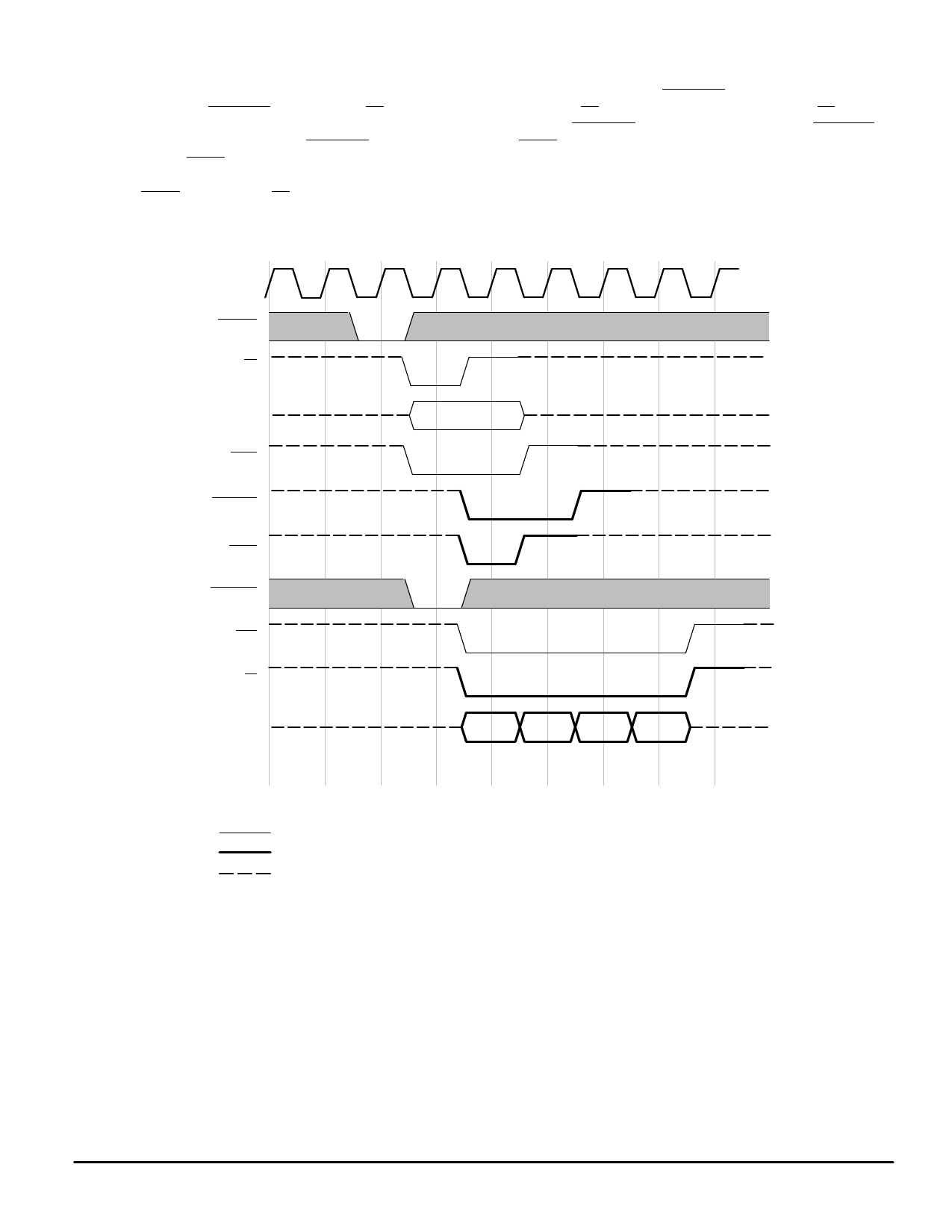

READ HIT/WRITE HIT

Figure 1 shows a read hit from an idle bus state. The

MPC2605 asserts L2 CLAIM the cycle after TS to inform the

memory controller that there is a cache hit and the cache will

control the rest of the transaction. L2 CLAIM is held through

the cycle after AACK is asserted. Since there are no active

data tenures from previous transactions, the MPC2605

asserts AACK the cycle after TS is asserted. Note there must

be a qualified assertion of CPU DBG in the same cycle as the

assertion of TS for the MPC2605 to respond with TA in the

next cycle. CPU DBG does not affect the timing of L2 CLAIM

or AACK.

The write hit timing is virtually the same. The only dif-

ference is the processor drives the data instead of the

MPC2605.

CLK

CPU BG

TS

1

2

3

4

5

6

A0 – A31

A

TBST

L2 CLAIM

AACK

CPU DBG

DBB

TA

DH0 – DH31,

DL0 – DL31

A1

A2

A3

A4

LEGEND

Signal driven to the MPC2605

Signal driven by the MPC2605

High–Z

Figure 1. Burst Read (or Write) Hit

MOTOROLA

MPC2605

15